# Master–Slave Current-Sharing Control of a Parallel DC–DC Converter System Over an RF Communication Interface

Sudip K. Mazumder, Senior Member, IEEE, Muhammad Tahir, Student Member, IEEE, and Kaustuva Acharya, Student Member, IEEE

Abstract—Using analog wireless communication, we demonstrate a master-slave load-sharing control of a parallel dc-dc buck converter system, thereby eliminating the need for physical connection to distribute the control signal among the converter modules. The current reference for the slave modules is provided by the master module using radio-frequency (RF) transmission, thereby ensuring even sharing of the load current. The effect of delay due to RF transmission on system stability and performance is analyzed, and regions of operation for a stable as well as satisfactory performance are determined. We experimentally demonstrate a satisfactory performance of the master-slave converter at 20-kHz switching frequency under steady state as well as transient conditions in the presence of a transmission delay. The proposed control concept, which can potentially attain redundancy that is achievable using a droop method, may lead to more robust and reconfigurable control implementation of distributed converters and power systems. It may also be used as a (fault-tolerant) backup for wire-based control of parallel/distributed converters.

*Index Terms*—Load sharing, master-slave control, parallel dc-dc converter, time delay effects, time-delayed system stability, wireless-network-based control.

# I. INTRODUCTION

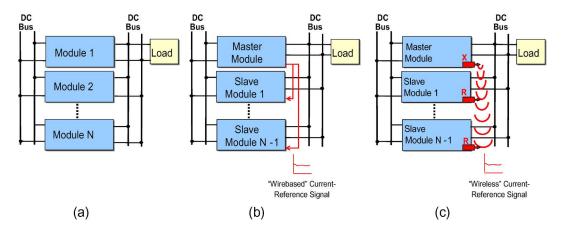

OAD-SHARING parallel dc—dc converters potentially offer several advantages over a single standalone unit in terms of modular architecture, reconfigurability, redundancy and fault tolerance, and cost. However, the reliability of such distributed systems relies heavily on their ability to share the power equally during steady state as well as transient conditions. One of the commonly used methods for stabilization of parallel dc—dc converters is the conventional droop method [1], [2], which is shown in Fig. 1(a). Load sharing among the power supplies using the droop method is dependent on the output-voltage setting of each power converter and may be compromised if a tight voltage regulation is desired. Active current-sharing mechanisms [3]—[7] provide a better alternative

Manuscript received May 6, 2006; revised September 25, 2007. This work was supported in part by the National Science Foundation (NSF) CAREER Award 0239131 and by the Office of Naval Research (ONR) Young Investigator Award N000140510594 received by Prof. Mazumder in 2003 and 2005, respectively.

The authors are with the Laboratory for Energy and Switching-Electronics Systems, Department of Electrical and Computer Engineering, University of Illinois, Chicago, IL 60607 USA (e-mail: mazumder@ece.uic.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2007.896138

to conventional droop methods by monitoring the difference between the reference current (which, for instance, could be the average of the currents of all parallel modules or the current of a dedicated or democratic master) and the output (or inductor) current of each converter module and incorporate this information into the control loop. One common current-sharing approach is the dedicated master–slave control scheme, as shown in Fig. 1(b), which ensures that all of the slave modules follow the reference current of the master. However, traditional current-sharing mechanisms rely on a physical connection among the converter modules; hence, system redundancy and reconfigurability may be compromised.

A radio-frequency (RF)-based wireless-network control of power electronic converters has been proposed in [8]-[10], which can be used to achieve a level of redundancy that is close to that of the droop method, while ensuring that the load-sharing performance and voltage regulation of the system are not compromised. In [8], a pulsewidth modulated (PWM) signal-sharing mechanism (over a digital link) for a parallel dc-dc converter is demonstrated. However, the bandwidth is limited due to the lack of current-sharing loops. In this paper, we propose a dedicated master-slave control scheme based on information transfer over a wireless communication link from the master module to the slave, as shown in Fig. 1(c). The effectiveness of the wireless-network-control scheme is demonstrated for a switching frequency of 20 kHz and for a channel separation of approximately 3 ft. Furthermore, we determine the impacts of RF communication delay [11], [12] on the stability and performance of the parallel converter, with focus on the following:

- 1) reaching condition for orbital existence (which predicts convergence to an orbit from any arbitrary initial condition during transients/start-up [13]);

- 2) steady-state stability;

- 3) load-sharing performance.

For 1), we use a nonlinear technique based on multiple-Lyapunov functions, which is described by the authors in [14] and [15]. For 2), we use a linearized average model and frequency domain techniques, presented in [16]. For 3) we use time-domain simulations during steady state and transients. These analysis techniques are used to obtain the bounds for the time delays, which ensure that the stability and performance of the parallel converter are not compromised.

Fig. 1. Paralleling schemes for dc–dc converter. Wire-based (a) droop and (b) master–slave methods for distributing the current-reference signal of the master module among the N-1 slave modules. (c) Wireless master–slave current-sharing method, where the RF transmitter and receiver are represented, respectively, by the symbols X and R.

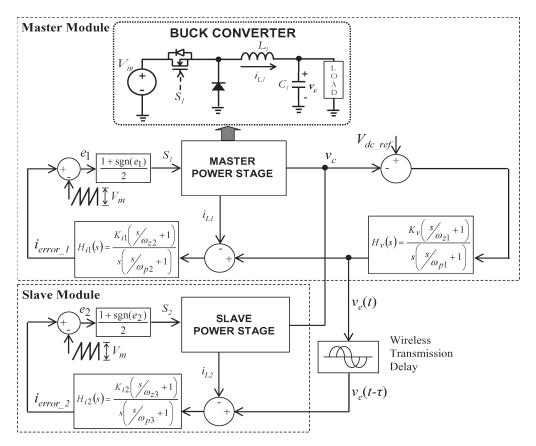

Fig. 2. Block diagram of the parallel dc-dc buck converter with wireless master-slave load-sharing control scheme. The slave module only has a current loop; the reference for its current loop is transmitted wirelessly from the master module using an analog RF transmitter block.

# II. CONTROL SCHEME AND STABILITY ANALYSIS

The control scheme for load-sharing dc—dc buck converters with N-modules connected in parallel is shown in Fig. 2. The controller for the master module has two control loops: voltage and current loops. The output of the voltage loop acts as the reference for the current loop. All the slave modules have the same controller structure and receive the current reference from the master module. In this section, we demonstrate the control design and stability analyses for a converter with two parallel-

connected modules. The analyses can be further extended to a higher number of modules by appropriately changing the system models.

The transfer functions of the voltage- and current-loop compensators of the master module are  $H_v(s)$  and  $H_{i1}(s)$ , respectively. The gain of the voltage loop  $(K_v)$  affects voltage regulation of the system (with variations in the load, input, and power-stage parameters) and current reference of the modules. The gain of the current loop  $(K_{i1})$  is tuned to achieve a

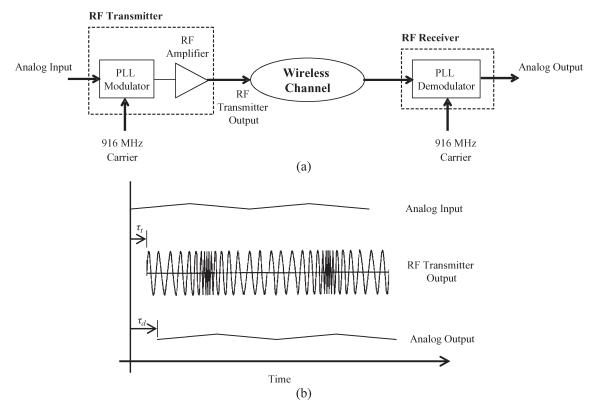

Fig. 3. Frequency-modulated RF transmission of the current-reference signal. (a) Block diagram for the transmitter, channel, and receiver. (b) Signal waveforms at the input of the transmitter (Analog Input), modulated signal at the output of the transmitter (RF Transmitter Output), where the maximum magnitude of the analog input signal corresponds to the maximum frequency but is delayed by the transmission delay  $\tau_t$ , and the demodulated signal at the receiver output (Analog Output) which is delayed by a total delay of  $\tau_d$ .

good transient response. The poles and zeros of the controllers are chosen so as to ensure that the closed-loop system has an adequate bandwidth and phase margin. The output of the current loop, which is an error signal, is passed through a comparator, whose other input is a ramp signal. The output of the comparator is the PWM signal, which (after passing it through a gate driver) is used to control the power MOSFET of the buck converter. The frequency of the ramp signal determines the switching frequency of the converter.

For N=2, the transfer function of the current loop of the slave module is given by  $H_{i2}(s)$ . The reference for this controller is generated by the voltage loop of the master. This ensures that the current distribution between the two modules is even, thus alleviating problems associated with unequal load sharing among the converter modules. However, any mismatch in the current reference of the two modules (due to transmission error or delay from the master to the slave module) can lead to a load-sharing error. Because the gain of the voltage loop determines the current reference for the master and slave modules, it affects the dynamics and performance of the load-sharing converter. The current reference of the master module is transmitted to the slave module through a wireless communication channel. To achieve this, first, the current-reference signal of the master is fed to an RF transmitter on the master module. The RF transmitter broadcasts it after modulating the signal using a high-frequency carrier, as shown in Fig. 3. Subsequently, the transmitted signal is captured by the receiver antenna, which is tuned to RF transmission frequency as well. The receiver demodulates and tunes the received current-reference signal such that it closely matches the current-reference signal of the master. This current-reference signal is then fed to the current loop of the slave module. The wireless channel is modeled as a single delay (comprising transmission, propagation, and reception delays). Delay due to propagation is relatively small for channel lengths lesser than 100 ft. An increase in the switching frequency results in an increase in the phase lag between the master and slave controller outputs. By assuming that  $\tau_d$  is the time delay from the master module to the slave module and that  $f_s$  is the switching frequency, then the phase lag between the two modules is given by  $\Delta \phi = f_s \times \tau_d$ .

To investigate the impacts of time delay on the dynamics of the parallel buck converter, we consider two modes of operation. First, we investigate the reaching conditions for orbital existence of the converter using a piecewise-linear model of the system [14], [15]. Such analyses can be used to determine if the state-trajectories of the parallel converter converge to an orbit in the presence of time-delays due to the wireless communication network. The state-space equation of this system can be expressed as

$$\dot{x}(t) = A_{0i}x(t) + A_{1i}x(t - \tau_d) + B_i \tag{1}$$

where *i* denotes the switching state of the system,  $x = \begin{bmatrix} i_{L1} & i_{L2} & v_C & \xi_1 & \xi_2 & \xi_3 & \xi_4 & \xi_5 & \xi_6 \end{bmatrix}^T$  is the state of the

converter, and  $\tau_d$  is the time delay among the states.  $A_{0i}$ ,  $A_{1i}$ , and  $B_i$ , which are shown at the bottom of the page, depend on the switching states. For the two-module parallel buck converter, i can take any value from 0 to  $(2^2-1=3)$  depending on the output of the feedback controllers  $(i_{\rm error\_1}$  and  $i_{\rm error\_2})$ . The switching states of the converter can be expressed as

$$S_k(t) = \begin{cases} 0, & i_{\text{error}\_k}(t) \le V_{\text{mod}} \\ 1, & i_{\text{error}\_k}(t) > V_{\text{mod}} \end{cases}, \qquad k = \{1, 2\}.$$

(2)

From this point onwards, we drop the notation of time, and an arbitrary time-delayed vector  $y(t-\varphi)$  is represented as  $y_\varphi$  or  $y(t+\varphi)$  as  $y_{-\varphi}$ . We transform (1) to the error coordinates using  $e=x^*-x$ , where  $x^*$  is the desired value of the states. The modified state-space equations in the error coordinates can be expressed as

$$\dot{e} = A_{0i}e + A_{1i}e_{\tau_d} - (A_{0i} + A_{1i})x^* - B_i.$$

(3a)

Equation (3a) can be rewritten as

$$\dot{e} = (A_{0i} + A_{1i})e + A_{1i}(e_{\tau_d} - e) - (A_{0i} + A_{1i})x^* - B_i.$$

(3b)

$$^1(i\!=\!0)\!:\!(S_1\!=\!0,S_2\!=\!0);\;\;(i\!=\!1)\!:\!(S_1\!=\!1,S_2\!=\!10);\;\;(i\!=\!2)\!:\!(S_1\!=\!0,S_2\!=\!1);\;\text{and}\;(i\!=\!3)\!:\!(S_1\!=\!1,S_2\!=\!1).$$

Using

$$e_{\tau_d} - e = -[e_{-\tau}]_{\tau = -\tau_d}^{\tau = 0}$$

$$= \int_{-\tau_d}^{0} \left( -(A_{0i} + A_{1i})e_{-\tau} - A_{1i}e_{(\tau_d - \tau)} + (A_{0i} + A_{1i})x^* + B_i \right) d\tau$$

(3b) can be simplified to

$$\dot{e} = (A_{0i} + A_{1i})e - \int_{-\tau_d}^{0} A_{1i}A_{0i}e_{-\tau}d\tau - \int_{-2\tau_d}^{-\tau_d} A_{1i}^2e_{-\tau}d\tau + \overline{B}_i$$

(3c)

where  $\overline{B}_i = -B_i - (A_{0i} + A_{1i})x^* + \tau_d A_{1i}(B_i + (A_{0i} + A_{1i})x^*).$

The reaching condition of the system described by (3c) depends on the number of feasible nonrepetitive and non-redundant switching sequences [15]. For each of these switching sequences, we define a positive-definite quadratic composite Lyapunov function  $V_k(e)>0$  (for the kth switching sequence), which can be expressed as [17]

$$V_k(e) = \sum_{i=1}^h \alpha_{ki} e^{\mathrm{T}} P_{ki} e \tag{4}$$

$$B_i = \left[egin{array}{c} rac{S_1}{L_1}V_{

m in} \ rac{S_2}{L_2}V_{

m in} \ 0 \ V_{

m ref} \ 0 \ 0 \ 0 \ 0 \ 0 \end{array}

ight]$$

where h is the number of switching states in a given sequence,  $0 \le \alpha_{ki} \le 1$ ,  $\sum_{i=1}^h \alpha_{ki} = 1$ ,  $P_{ki} = P_{ki}^{\mathrm{T}}$  is a positive definite matrix, and  $pV_k(e) \ge V_k(e_\theta)$ , for any  $-\tau \le \theta \le 0$  and p > 1. The error trajectories of the system described by (3c) converge to the orbit if there exists  $P_{ki} > 0$ , such that  $V_k(t) < 0$ . To determine whether this condition is satisfied by (3c), we have a matrix inequality given by [14], [15]

$$\sum_{i=1}^{h} \alpha_{ki} \begin{bmatrix} M_{ki} & P_{ki}A_{1i}A_{0i} & -P_{ki}A_{1i}^{2} & P_{ki}\overline{B}_{i} \\ -A_{0i}^{\mathrm{T}}A_{1i}^{\mathrm{T}}P_{ki} & -pP_{ki} & 0 & 0 \\ -(A_{1i}^{2})^{\mathrm{T}}P_{ki} & 0 & -P_{ki} & 0 \\ \overline{B}_{i}^{\mathrm{T}}P_{ki} & 0 & 0 & 0 \end{bmatrix} < 0$$

(5)

where  $M_{ki} = (1/\tau_d) [P_{ki}(A_{0i} + A_{1i}) + (A_{0i} + A_{1i})^T P_{ki}] +$  $(p+1)P_{ki}$  [16]. This inequality can be solved using standard techniques for linear-matrix inequalities [18].

If there are no solutions to (5), we investigate the dual Lyapunov function to determine that the error trajectories of the converter do not converge to the orbit [19]. The dual Lyapunov function

$$\overline{V}_k = \sum_{i=1}^h \alpha_{ki} e^{\mathrm{T}} Q_{ki} e. \tag{6}$$

The error trajectories of the converter do not converge to the orbit, provided that

$$\sum_{i=1}^{h} \alpha_{ki} \begin{bmatrix} N_{ki} & -Q_{ki}A_{1i}A_{0i} & Q_{ki}A_{1i}^2 & -Q_{ki}\overline{B}_i \\ A_{0i}^T A_{1i}^T Q_{ki} & pQ_{ki} & 0 & 0 \\ (A_{1i}^2)^T Q_{ki} & 0 & Q_{ki} & 0 \\ -\overline{B}_i^T Q_{ki} & 0 & 0 & 0 \end{bmatrix} < 0 \quad \text{then } \overline{\tau} := \min_{1 \le i \le q} \overline{\tau}_i, \text{ and the system in (8) is stable for all } \tau_d \in [0, \overline{\tau}) \text{ and becomes unstable at } \tau_d = \overline{\tau}. \text{ In (10)}, \\ \underline{\rho}(A_0, A_1) := \min\{|\lambda| \mid \det(A_0 - \lambda A_1) = 0\}, \text{ and } \lambda(A, B) \text{ is the generalized eigenvalue of the matrices } A \text{ and } B \end{bmatrix}$$

where  $N_{ki} = (1/\tau_d)[Q_{ki}(A_{0i} + A_{1i}) + (A_{0i} + A_{1i})^TQ_{ki}] +$  $(p+1)Q_{ki}$ . If there are no solutions to (5) and there exist solutions to (7), we conclude that the error trajectories of the system do not converge to the orbit.

When the power devices of all the converter modules switch periodically, we use an averaged model to analyze the stability of the system. The state-space averaged model of the system is described by

$$\dot{x} = A_0 x + A_1 x (t - \tau_d) + B \qquad y = Cx$$

(8)

where  $x = [\widetilde{i}_{L1} \ \widetilde{i}_{L2} \ \widetilde{v}_C \ \xi_1 \ \xi_2 \ \xi_3 \ \xi_4 \ \xi_5 \ \xi_6]^{\mathrm{T}}, \ A_0 = A_{0i}, \ A_1 = A_{1i}, \ B = [(d_1/L_1)V_{\mathrm{in}} \ (d_2/L_2)V_{\mathrm{in}} \ 0 \ V_{\mathrm{ref}} \ 0 \ 0 \ 0 \ 0]^{\mathrm{T}}, \ C =$ [0 0 1 0 0 0 0 0]. Here,  $\widetilde{i}_{L1} = \langle i_{L1} \rangle$ ,  $\widetilde{i}_{L2} = \langle i_{L2} \rangle$ , and  $\widetilde{v}_c = \langle v_c \rangle$  are the average values for the states. The duty ratios of the switches  $d_1 = \langle S_1 \rangle$  and  $d_2 = \langle S_2 \rangle$  determined by the feedback controllers, as shown in Fig. 2, are given by

$$d_{1} = \frac{i_{\text{error}\_1}}{V_{m}} = \begin{bmatrix} K_{i1} & K_{i1}\omega_{z2} \\ V_{m} & V_{m} \end{bmatrix} \begin{bmatrix} \xi_{3} \\ \xi_{4} \end{bmatrix}$$

$$d_{2} = \frac{i_{\text{error}\_2}}{V_{m}} = \begin{bmatrix} K_{i2} & K_{i2}\omega_{z3} \\ V_{m} & V_{m} \end{bmatrix} \begin{bmatrix} \xi_{5} \\ \xi_{6} \end{bmatrix}. \tag{9}$$

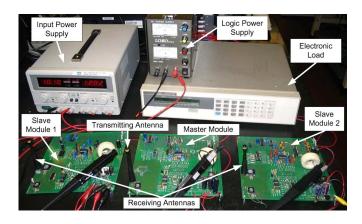

Fig. 4. Experimental setup comprising the master and two slave buck converter modules connected in parallel, logic and input power supplies, and an electronic load. The parallel power system implements dedicated master-slave current-sharing control using RF transmission.

The infinite-dimensional system in (8) with a single delay is stable if the delay  $\tau_d$  is below the delay bound  $\bar{\tau}$ . To determine how the delay bound  $\overline{\tau}$  varies with the gain of the voltage controller, we use a delay-dependent stability criterion, given in [16], which is summarized in the following.

Theorem<sup>2</sup>: For the system in (8) stable at  $\tau_d = 0$ , i.e.,  $A_0 +$  $A_1$  is stable and rank $(A_1) = q$ , we define

$$\overline{\tau}_i := \begin{cases} \min_{1 \leq k \leq n} \frac{\theta_k^i}{\omega_k^i}, & \text{if } \lambda_i \left( j \omega_k^i I - A_0, A_1 \right) = e^{-j\theta_k^i} \\ & \text{for some } \omega_k^i \in (0, \infty), \, \theta_k^i \in [0, 2\pi] \\ \infty, & \text{if } \underline{\rho}(j \omega I - A_0, A_1) > 1 \quad \forall \omega \in (0, \infty) \end{cases}$$

$\rho(A_0, A_1) := \min\{|\lambda| \mid \det(A_0 - \lambda A_1) = 0\}, \text{ and } \lambda(A, B) \text{ is }$ the generalized eigenvalue of the matrices A and B.

To use the aforementioned theorem, we devise an algorithm to compute the delay margin and also check whether the system is stable independent of delay. We first test the condition

$$\rho(j\omega I - A_0, A_1) > 1 \qquad \forall \omega \in (0, \infty). \tag{11}$$

If the condition in (11) is satisfied for all values of  $\omega$ , then the system is stable independent of delay. If there is some  $\omega$  for which the condition in (11) is not satisfied, using that value, we solve  $\lambda_i(j\omega I - A_0, A_1) = e^{-j\theta}$  for  $\theta$  and find the corresponding delay using (10).

### III. RESULTS

Fig. 4 shows an experimental setup for the master–slave buck converter for a three-module system. The power-stage, control, and wireless-transmission parameters for the experimental parallel converter are shown in Table I. The difference in the inductance of the master and slave modules (less than 10%) is

<sup>&</sup>lt;sup>2</sup>This theorem and its proof are given in [16].

| Nominal Parameters                                 | Values            | Nominal Parameters                                                   | Values          |

|----------------------------------------------------|-------------------|----------------------------------------------------------------------|-----------------|

| Switching frequency                                | 20 kHz            | Ramp height                                                          | 8 V             |

| Bandwidth of the wireless transmitter and receiver | 28 kHz            | DC gain $(K_v)$ of the master voltage loop                           | 3000            |

| Channel separation attempted so far                | 10 feet           | Zero $(w_{zl})$ of the master voltage loop compensator               | 500 rad/s       |

| Wireless transmitter to receiver delay             | 20 μS             | Pole $(w_{pl})$ of the master voltage loop compensator               | 20,000<br>rad/s |

| Output inductance of the master                    | 155 μΗ            | DC gain $(K_{il}, K_{i2})$ of the master/slave current loop          | 4000            |

| Output inductance of the slaves                    | 165 μH,<br>162 μH | Zero $(w_{z2}, w_{z3})$ of the master/slave current loop compensator | 1000<br>rad/s   |

| Output capacitance                                 | 800 μF            | Pole $(w_{p2}, w_{p3})$ of the master/slave current loop compensator | 25,000<br>rad/s |

| Reference output voltage for the master            | 2.5 V             | Logic power supply for the master and slave boards                   | ±15V<br>and 5V  |

| Input voltage                                      | 10 V              | Regulated output voltage                                             | 5 V             |

TABLE I

PARAMETERS OF THE MASTER–SLAVE PARALLEL BUCK CONVERTER

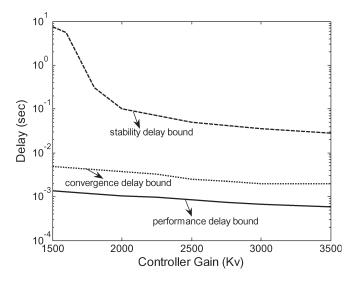

Fig. 5. Delay bound for the system to operate in stable region, to converge to the switching surface, and to meet the performance criterion (5% load-sharing error among the modules) for different values of voltage loop controller gain  $(K_v)$ .

due to small variations in the parameters of the cores and the nature of the windings. First, we examine whether the converter satisfies the reaching conditions for orbital existence. Using the conditions given in (5) and (7), we determine the bounds of the time delay for the system dynamics to converge to the orbit. Fig. 5 shows the variation of such a bound with the gain of the voltage-loop compensator. When the converter switches periodically, we use a linearized averaged model to analyze the stability of the system. For the system described by (8),  $\operatorname{rank}(A_1) = 1$ , and  $\overline{\tau} = \overline{\tau}_1$ . To find  $\overline{\tau}_1$  using the criterion in (10), we sweep the frequency from  $\infty \to 0$  and find the points at which  $\rho(j\omega I - A_0, A_1) \approx 1$ . Using this value of  $\omega$  and the

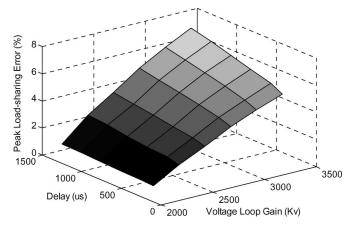

Fig. 6. Variation of peak load-sharing error with variation in the voltage loop gain and time delay between the master and slave modules.

fact that there is only one nonzero generalized eigenvalue for the system considered in this paper, we have  $\omega=\omega_1^1$ . Next, we find the delay threshold as  $\min_{1\leq k\leq n}\theta_k^1/\omega_k^1$  by varying  $\theta_k^1$  in the interval of  $[0,2\pi].$  For example, the delay threshold for  $K_v=3000$  is  $\overline{\tau}_1=\theta_1^1/\omega_1^1=2.085/58.748=35.5$  ms. The time-delay bound for the system to operate in stable region at different values of the voltage controller gain is shown in Fig. 5. For the present case, this delay bound is larger than the delay bound for the system to converge to the switching surface during start-up and transient conditions.

In Fig. 6, we investigate the impact of the RF transmission delay on the performance of the load-sharing control system. We observe that the maximum difference between the output current of the converter modules under transient condition (referred to as the peak load-sharing error) increases with increasing RF transmission delay. However, for a given

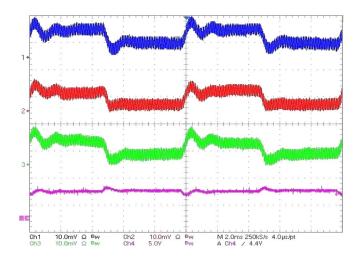

Fig. 7. Output voltage (Ch4) and master and slave inductor currents (Ch1, Ch2, and Ch3), respectively, during load-transient. The load-transient specifications are tabulated in Table II.

TABLE II SPECIFICATIONS OF THE LOAD-TRANSIENT

| Nominal Parameters                | Values |

|-----------------------------------|--------|

| Time period of the load-transient | 10 ms  |

| Duty ratio of the load-transient  | 50%    |

| Minimum value of the load current | 1 A    |

| Maximum value of the load current | 3.0 A  |

RF transmission delay, the peak load-sharing error can be reduced by reducing the master module's voltage-loop dc gain  $(K_v)$ , which directly affects the current reference for the slave module. For a maximum tolerable load-sharing error of 5%, the bounds for the time-delay are shown in Fig. 5 along with the bounds for convergence and stability. This time-delay bound could vary depending on the other operating criteria of the parallel converters. Clearly, the time-delay bound for the performance criteria is the lowest and hence can be used to determine the operating delay limits of the system.

Fig. 7 shows the experimental validation of the theoretical results under a load transient condition with an RF transmission delay ( $\tau_d$ ) of 20  $\mu$ s. We subject the master–slave converter system to a load transient; the details of which are tabulated in Table II. Fig. 7 shows the output voltage and the inductor currents of the master and two slave modules. The inductor currents of the slave modules track the corresponding signal of the master well, despite the variation in the inductance of the slave modules.

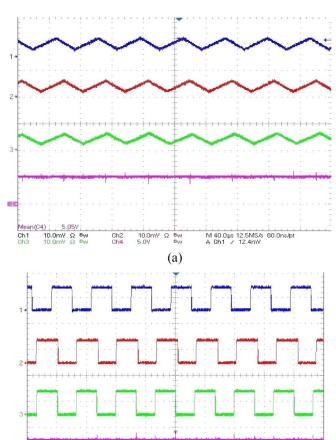

The steady-state performances of the parallel converter are shown in Fig. 8. Fig. 8(b) shows the gate-driver signals of the master and slave modules along with the output voltage. Fig. 8(a) shows that both the master and slave modules are regulated at 5 V and that the mean values of the three inductor currents are close, establishing that the master and two slave modules share the load current evenly. The ripple current of the

Fig. 8. Steady-state performance of the master–slave converter system. (a) Inductor current (2 A/div) of the master (Ch1) and slave modules (Ch2 and Ch3) along with the output voltage (Ch4). We note that the input to Ch1–Ch3 (which is set at 20 mV/div) is the output of a hall-sensor current amplifier, which is set at 2 A/div. (b) Gate-driver signals (Ch1, Ch2, and Ch3) for the master and slave modules and the inverter output voltage.

(b)

slave modules is slightly lower (than that of the master module) because of its higher inductance.

## IV. SUMMARY AND CONCLUSION

We demonstrate the effectiveness of an analog wireless master–slave current-sharing control of a parallel dc–dc buck converter under transient and steady-state conditions. Unlike the wireless PWM scheme described in [8], the active-current-sharing scheme, described in this paper, yields better dynamic response and mitigates the possibility of steady-state error in [8] due to RF transmitter nonlinearities. Using multiple-Lyapunov and eigenvalue approaches, this paper also analyzes the reaching conditions for orbital existence and steady-state stability, respectively, of the load-sharing converters in the presence of communication delay. Our analyses yield the time-delay bounds for stability and performance of the system. If the system operates within these prescribed bounds, the proposed control scheme can be used to achieve a high level of redundancy (of a droop method) while ensuring a satisfactory

steady-state and transient performance of wire-based activecurrent-sharing schemes. The proposed distributed control can be extended to multimodule parallel and networked converters as a primary or as a fault-tolerant backup control.

### ACKNOWLEDGMENT

Any opinions, findings, conclusions, or recommendations expressed herein are those of the authors and do not necessarily reflect the views of the NSF and the ONR.

### REFERENCES

- K. Siri, "Analysis and design of distributed power systems," Ph.D. dissertation, Dept. Elect. Eng., Univ. Illinois, Chicago, 1991.

- [2] C. Jamerson and C. Mullett, "Parallel supplies via various droop methods," in *Proc. High Freq. Power Convers. Conf.*, 1994, pp. 68–76.

- [3] V. J. Thottuvelil and G. C. Verghese, "Stability analysis of paralleled dc/dc converters with active current sharing," in *Proc. IEEE Power Electron. Spec. Conf.*, 1996, pp. 1080–1086.

- [4] G. Garcera, M. Pascual, and E. Figueres, "Robust average current-mode control of multi-module parallel dc-dc PWM converter systems with improved dynamic response," *IEEE Trans. Ind. Electron.*, vol. 48, no. 5, pp. 995–1005, Oct. 2001.

- [5] J. Rajagopalan, K. Xing, Y. Guo, and F. C. Lee, "Modeling and dynamic analysis of paralleled dc/dc converters with master–slave current sharing control," in *Proc. IEEE Appl. Power Electron. Conf.*, 1996, pp. 678–684.

- [6] S. K. Mazumder, A. H. Nayfeh, and D. Boroyevich, "Robust control of parallel dc-dc buck converters by combining integral-variable-structure and multiple-sliding-surface control schemes," *IEEE Trans. Power Electron.*, vol. 17, no. 3, pp. 428–437, May 2002.

- [7] S. K. Mazumder, A. H. Nayfeh, and D. Boroyevich, "Stability analysis of parallel dc–dc converters using a nonlinear approach," in *Proc. IEEE Power Electron. Spec. Conf.*, 2001, pp. 1283–1288.

- [8] S. K. Mazumder, M. Tahir, and S. L. Kamisetty, "Wireless PWM control of a parallel dc-dc buck converter," *IEEE Trans. Power Electron.*, vol. 20, no. 6, pp. 1280–1286, Nov. 2005.

- [9] S. K. Mazumder, K. Acharya, and M. Tahir, "Wireless control of spatially distributed power electronics," in *Proc. IEEE Appl. Power Electron. Conf.*, Mar. 2005, pp. 75–81.

- [10] K. Acharya, S. K. Mazumder, and M. Tahir, "Communication fault-tolerant wireless network control of a load-sharing multiphase interactive power network," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 2006, pp. 1167–1174.

- [11] P. Marti, J. Yepez, M. Velasco, R. Villa, and J. M. Fuertes, "Managing quality-of-control in network-based control systems by controller and message scheduling co-design," *IEEE Trans. Ind. Electron.*, vol. 51, no. 6, pp. 1159–1167, Dec. 2004.

- [12] G.-P. Liu, Y. Xia, J. Chen, D. Rees, and W. Hu, "Networked predictive control of systems with random network delays in both forward and feedback channels," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1282– 1297, Jun. 2007.

- [13] D. Casadei, J. Clare, L. Empringham, G. Serra, A. Tani, A. Trentin, P. Wheeler, and L. Zarri, "Large-signal model for the stability analysis of matrix converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 939– 950, Apr. 2007.

- [14] S. K. Mazumder and K. Acharya, "Multiple Lyapunov function based reaching condition analyses of switching power converters," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 2006, pp. 2232–2239.

- [15] S. K. Mazumder and K. Acharya, "Global stability analyses of switching power converters," in *Proc. IEEE Power Electron. Spec. Conf.*, Orlando, FL, Jun. 2007. Tutorial.

- [16] K. Gu, V. L. Kharitonov, and J. Chen, Stability of Time Delay Systems. Boston, MA: Birkhauser, 2003.

- [17] M. Johansson, "Piecewise linear control systems," Ph.D. dissertation, Lund Inst. Technol., Lund, Sweden, 1999.

- [18] S. Boyd, L. El Ghaoui, E. Feron, and V. Balakrishnan, *Linear Matrix Inequalities in System and Control Theory*. Philadelphia, PA: SIAM, 1994.

- [19] R. Goebel, T. Hu, and A. R. Teel. (2005, Dec.). "Dual matrix inequalities in stability and performance analysis of linear differential/difference inclusions," in *Current Trends in Nonlinear Systems and Control*. Boston, MA: Birkhauser. [Online]. Available: http://faculty.uml.edu/thu/dmi.pdf

**Sudip K. Mazumder** (SM'02) received the Ph.D. degree from Virginia Polytechnic Institute and State University, Blacksburg, in 2001.

He has more than 12 years of professional experience and has held R&D and design positions in leading industrial organizations. He is currently the Director of the Laboratory for Energy and Switching-Electronics Systems and a tenured Associate Professor with the Department of Electrical and Computer Engineering, University of Illinois, Chicago (UIC). Under his leadership, UIC received

the Third Place in the 2005 IEEE International Future Energy Challenge Fuel Cell Energy Student Competition, and one of his Ph.D. students received the 2007 Joseph J. Suozzi INTELEC Fellowship in Power Electronics. Since 2006, he has been the Editor in Chief of the *International Journal of Power Management Electronics*.

Prof. Mazumder received the IEEE TRANSACTIONS ON POWER ELECTRONICS AND INDUSTRIAL ELECTRONICS Prize Paper Award in 2002, a National Science Foundation Faculty Early Career Development Award in 2003, the Young Investigator Award from the Office of Naval Research in 2005, and the Diamond Award from the University of Illinois in 2006 for his outstanding performance in power electronics research. He is also a corecipient (with his student M. Tahir) of the Outstanding Student Paper Award in the 21st IEEE International Conference on Advanced Information Networking and Applications (AINA 2007). From 2002 to 2005, he was an Associate Editor for the IEEE POWER ELECTRONICS LETTERS. Since 2003, he has been an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS. He was the Publications Chair of the IEEE Power Electronics Society in 2003. He was a Tutorial Cochair of the 38th IEEE Power Electronics Specialists Conference (PESC 2007). He has been invited for plenary and keynote lectures, including the Fourth IEEE India International Conference on Power Electronics (IICPE 2006), PESC 2006, ASME 2005, and the Ninth IEEE International Power Electronics Congress (CIEP 2004). He was also invited by the Office of Naval Research and the Defense Advanced Research Projects Agency for a presentation on the future of power electronics in 2005 and by the Department of Energy and the National Institute of Standards and Technology for an invited presentation on high-power fuel cell inverters in 2007.

Muhammad Tahir (S'03) received the B.Sc. degree in electrical engineering and the M.Sc. degree in computer engineering from the University of Engineering and Technology, Lahore, Pakistan, in 1999 and 2003, respectively. He is currently working toward the Ph.D. degree in the Laboratory for Energy and Switching-Electronics Systems, Department of Electrical and Computer Engineering, University of Illinois, Chicago.

From 2000 to 2003, he was a Lecturer in the Department of Electrical Engineering, University of

Engineering and Technology. His research interests include distributed optimization of wireless network resources for network control of high-frequency switching systems and the analysis of time-delay systems.

Mr. Tahir is the corecipient of the Outstanding Student Paper Award in the 21st IEEE International Conference on Advanced Information Networking and Applications (AINA 2007).

**Kaustuva Acharya** (S'06) received the B.Eng. degree in electronics and communication engineering from the Regional Engineering College (now the National Institute of Technology), Bhopal, India, in 2000 and the M.Sc. degree in electrical engineering from the University of Illinois, Chicago, in 2003. He is currently working toward the Ph.D. degree in electrical engineering in the University of Illinois.

He is a Research Assistant at the Laboratory for Energy and Switching-Electronics Systems, Department of Electrical and Computer Engineering, Uni-

versity of Illinois. He has published more than 15 refereed international journal papers and conference proceedings. His research interests include power electronics for renewable and alternate energy sources and the modeling, analyses, and control of interactive power networks for distributed power systems.

Mr. Acharya is a Reviewer for the IEEE TRANSACTIONS ON POWER ELECTRONICS AND INDUSTRIAL ELECTRONICS and several international conferences.