# A Soft-Switched Hybrid-Modulation Scheme for a Capacitor-Less Three-Phase Pulsating-DC-Link Inverter

Arash Rahnamaee, Student Member, IEEE, and Sudip K. Mazumder, Senior Member, IEEE

Abstract-A soft-switched hybrid-modulation (HM) scheme is outlined for a dc-link-capacitor-less three-phase high-frequency (HF) pulsating-dc link (PDCL) isolated multistage inverter. The overall inverter comprises a front-end isolated dc/pulsating-dc converter followed by a pulsating-dc/ac converter. Because the two stages are directly connected without a dc-link capacitor, the intermediate link is a PDCL instead of a fixed-dc link as in conventional HF-link inverters. The HM modulates the pulsating-dc/ac converter such that, two of its converter legs are line-switched, while the third leg of the pulsating-dc/ac converter is switched under zero-voltage-switching condition. This is achieved by first modulating the dc/pulsating-dc converter to achieve a specific encoding of the PDCL signal, which in turn, is exploited by the modulation scheme of the pulsating-dc/ac converter to mitigate its switching loss without requiring any auxiliary circuit. Operation of the pulsating-dc/ac converter using the soft-switched HM scheme is validated using a prototype 1 kW, 72-V (dc)/208-V (ac) HF inverter.

*Index Terms*—Capacitor-less, high-frequency (HF) link, hybrid modulation, inverter, pulsating-dc link (PDCL), soft switching, three phase.

#### I. INTRODUCTION

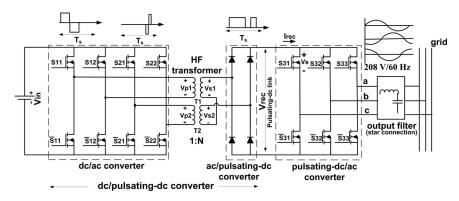

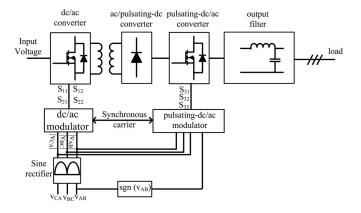

pulsating-dc link (PDCL) high-frequency (HF) inverter topology is suitable for multiple applications including solar energy, fuel-cell energy, wind energy, energy storage, electrical vehicles, and power quality. It yields high power density due to elimination of line-frequency (LF) transformers with HF transformers and elimination of dc-link. Fig. 1 shows a simplified structure of a PDCL HF inverter that consists of two conversion stages: 1) a dc/pulsating-dc converter that comprises dc/ac converters, HF transformers, and an ac/pulsating-dc converter; and 2) a pulsating-dc/ac converter that generates the desired LF output ac voltages. Well-known sine-wave pulse-width modulation or space-vector modulation schemes can be used to derive the LF output ac voltages for single-phase and three-phase in-

Manuscript received March 8, 2013; revised May 7, 2013; accepted May 31, 2013. Date of current version March 26, 2014. This work is supported in part by the National Science Foundation (NSF) Awards (0936811, 1239118, 1002369) received by Prof. Sudip K. Mazumder at the University of Illinois, Chicago. However, any opinions, findings, conclusions, or recommendations expressed herein are those of the authors and do not necessarily reflect the views of the NSF. Recommended for publication by Associate Editor Y. Xue.

The authors are with the Laboratory for Energy and Switching Electronics Systems, Department of Electrical and Computer Engineering, University of Illinois at Chicago, Chicago, IL 60607 USA (e-mail: a.rahnamaee@gmail.com; mazumder@uic.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2013.2269141

verters [1]–[13]. However, multistage power conversion of the PDCL inverter requires a carefully designed switching scheme to reduce device losses of the inverter and ensure the synthesis of the inverter output waveforms with acceptable harmonic distortion.

One such modulation scheme is described in [14] that uses a square-wave modulation scheme. It uses the square-wave modulation for the dc/ac converter. Using such a modulation, the dc/ac converter generates a stream of pulses with fixed on-time width on the PDCL. As such, a sine-wave modulation technique must be applied to the pulsating-dc/ac converter to generate the line-frequency ac output voltages. Therefore, all the legs of the pulsating-dc/ac converter operate at HF under hard-switching condition. Discontinuous-modulation schemes [15]–[19] can reduce the switching loss of the pulsating-dc/ac converter by allowing no switching of one of the legs of the three-leg converter. Therefore, these schemes yield no commutation of a leg for a specific angular duration (e.g.,  $30^{\circ}$  or  $60^{\circ}$ ) of any line cycle. However, this still incurs HF switching of the remaining legs of the converter under hard-switching condition.

The originally proposed HM scheme (referred to as the conventional HM in this paper), described in [20]-[23], can be applied to the pulsating-dc/ac converter to decrease the switching requirements of the converter. Unlike the discontinuousmodulation schemes, the conventional HM scheme requires no HF commutation on two of the legs of the pulsating-dc/ac converter. Therefore, only one of the three legs operates under HF hard-switching condition. This additional reduction in switching is achieved by recognizing that, if the dc/ac converter switches are sinusoidally modulated (emulating the inverter output), the PDCL signal, representing the maximum (dc/ac-converter) phase-to-phase voltage, is also encoded with this sinusoidal information, which is exploited by the HM to reduce switching need for the pulsating-dc/ac converter. Because the maximum phase-to-phase voltage of the dc/ac converter changes every 60° of the line cycle, the HM of the pulsatingdc/ac converter appropriately selects the two converter legs that are not switched in this 60° interval. Notwithstanding, switching loss incurred in the remaining converter leg that is hard-switched needs to be addressed.

As such, in this paper, a soft-switched HM scheme is developed to provide soft-switching condition for the pulsatingdc/ac converter. A novel and fundamentally different modulation scheme must be applied to the dc/ac converter to enable softswitched HM of the pulsating-dc/ac-converter switches. Using this scheme, the two predetermined legs of the pulsating-dc/ac

<sup>0885-8993 © 2013</sup> IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 1. Schematic of the PDCL HF inverter which operates using the soft-switched HM scheme.

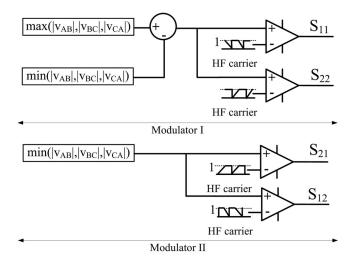

Fig. 2. Switching signal generation for the dc/ac converter (dc/ac modulator).

converter are not switched in every  $60^{\circ}$  of the line cycle while the other leg works at HF but under soft-switching condition. Therefore, soft-switched HM scheme proposes unique modulation mechanism for the dc/ac and the pulsating-dc/ac converters.

This paper consists of four additional sections. The principle of operation of the soft-switched HM scheme is outlined in Section II. Section III describes the modes of operation of the PDCL HF inverter (as shown in Fig. 1) using the soft-switched HM scheme. In Section III, key simulation and experimental results, obtained using a 1-kW prototype PDCL HF inverter, are presented to validate the performance of the soft-switched HM scheme. Finally, conclusions based on the novel HM scheme are outlined in Section IV.

# II. PRINCIPLE OF OPERATION

PDCL HF inverter consists of two active stages, which are the front-end dc/ac and pulsating-dc/ac converters. The dc/ac converter generates width modulated bipolar pulses for HF transformers. The modulated voltage pulses across the secondary sides of the HF transformers are rectified by the ac/pulsating-dc converter to generate the PDCL waveform. An RCD snubber [24] is used to limit the voltage spikes on the PDCL waveform due to the leakage inductances of the HF transformers and parasitic output capacitors of the ac/pulsating-dc converter.

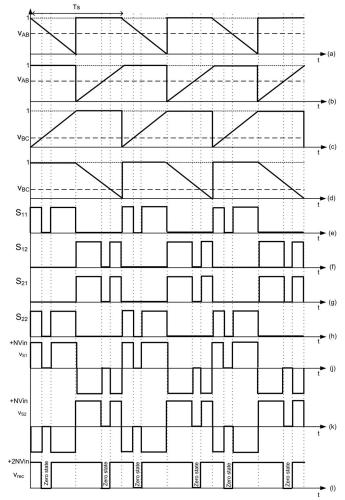

Fig. 3. Pulse placement on the PDCL using the dc/ac converter to provide zero states: (a)–(d) the HF carriers and references of the full-bridge modules of the dc/ac converter to generate bipolar pulses for HF transformers, (e)–(h) the synthesized gate signals of  $S_{11}$ ,  $S_{21}$ ,  $S_{21}$ , and  $S_{22}$ , (j)–(k) the secondary voltages of the HF transformer, and (l) the generated PDCL waveform.

Finally, the pulsating-dc/ac converter generates the LF output sine-waves using the pulses on the PDCL waveform. Therefore, the PDCL waveform is synthesized by the dc/ac converter and the pulsating-dc/ac converter uses the synthesized pulses on the PDCL waveform to generate LF output sine-wave pulses. The soft-switched HM scheme decreases the switching losses

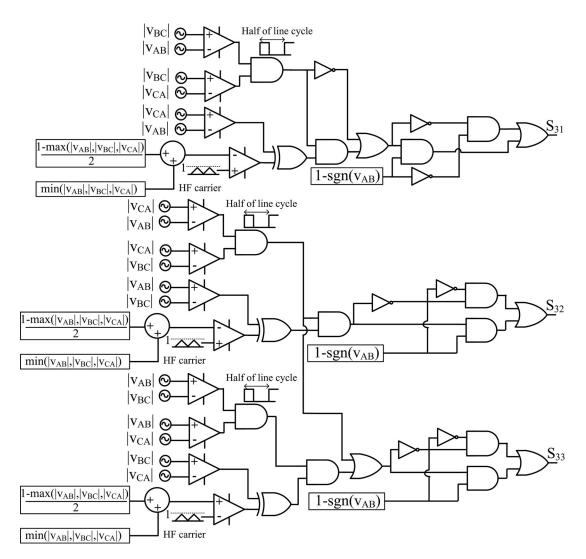

Fig. 4. Switching signals generation for the pulsating-dc/ac converter.

Fig. 5. Simplified operation overview of the PDCL HF inverter using the soft-switched HM.

of the pulsating-dc/ac converter by decreasing the switching requirement and ZVS operation of the pulsating-dc/ac converter. This section explains the modulation scheme to synthesize the PDCL waveform, then; the soft-switched HM for pulsating-dc/ac converter to yield the desired LF output sine-waves.

# A. Synthesis of the PDCL Waveform

The dc/ac converter generates two sets of bipolar pulses for the HF transformers to avoid core saturation. The PDCL HF inverter has two full-bridge modules operating as a dc/ac converter. The first full-bridge module includes  $S_{11}$ ,  $\bar{S}_{11}$ ,  $S_{12}$ , and  $\bar{S}_{12}$ . The second full-bridge module (using modulator II) includes  $S_{21}$ ,  $\bar{S}_{21}$ ,  $S_{22}$ , and  $\bar{S}_{22}$ . Each full-bridge module generates a set of bipolar pulses for a HF transformer. Two switches of each leg operate complementary and a proper dead-time is considered to avoid short-circuit of the input dc bus. Fig. 2 shows the modulation scheme for switching signal generation of the dc/ac converter. A set of normalized three-phase sine-wave references are defined as (1)

$$v_{AB} = m * \sin(\omega t)$$

$$v_{BC} = m * \sin\left(\omega t + \frac{2\pi}{3}\right)$$

$$v_{CA} = m * \sin\left(\omega t + \frac{4\pi}{3}\right)$$

(1)

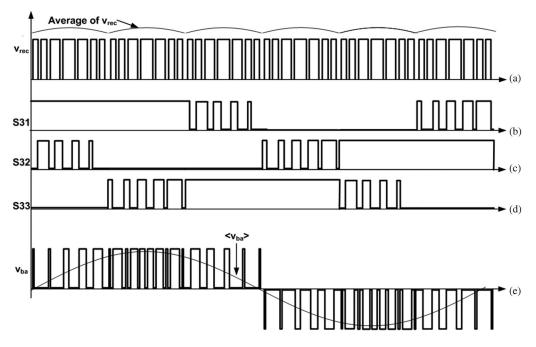

Fig. 6. Switching functions and waveforms of the soft-switched HM pulsating-dc/ac converter: (a) PDCL, (b)–(d) gate signals of pulsating-dc/ac converter switches, and (e) resulting phase-to-phase voltage before and after the output filters.

Fig. 7. Equivalent circuit of the ac/pulsating-dc converter, HF transformers, and the front-end pulsating-dc/ac converter to study topological modes of operation.

where m is modulation index and  $\omega$  is output line angular frequency of the LF output sine-waves. We also obtain the following relationships for a balanced system:

$$\begin{aligned}

v_{ij} + v_{jk} + v_{ki} &= 0 \\

v_{ij} &= -(v_{jk} + v_{ki})

\end{aligned}

(2)$$

where  $i, j, k \underset{i \neq j \neq k}{\in} \{A, B, C\}$ . One can conclude

$$v_{ij} = |v_{jk} + v_{ki}|. (3)$$

Then, following equation are obtained for different  $60^{\circ}$  sectors of the output line cycle:

$$|v_{CA}| = |v_{AB}| + |v_{BC}| \quad 0 < \omega t < \frac{\pi}{3} \text{ or for } \pi < \omega t < \frac{4\pi}{3}$$

(4)

$$|v_{AB}| = |v_{BC}| + |v_{CA}| \quad \frac{\pi}{3} < \omega t < \frac{2\pi}{3} \text{ or for } \frac{4\pi}{3} < \omega t < \frac{5\pi}{3}$$

(5)

$$|v_{BC}| = |v_{CA}| + |v_{AB}| \quad \frac{2\pi}{3} < \omega t < \pi \text{ or for } \frac{5\pi}{3} < \omega t < 2\pi.$$

(6)

Therefore, the PDCL waveform is required to be compartmentalized in six distinct sectors; that is PI:  $0-60^{\circ}$ , PII:  $60^{\circ}-120^{\circ}$ , PIII:  $120^{\circ}-180^{\circ}$ , PIV:  $180^{\circ}-240^{\circ}$ , PV:  $240^{\circ}-300^{\circ}$ , and PVI:  $300^{\circ}-360^{\circ}$ . During each sector, the dc/ac converter generates two sets of pulses representing the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ . In each sector, the nonmaximum voltage reference signal is synthesized by two pulses representing two other nonmaximum reference signals as shown in (4)–(6). Therefore, the voltage reference signals of the dc/ac modulator change in every

Fig. 8. Key waveforms of the equivalent circuit shown in Fig. 7 to study the soft-switching operation of the pulsating-dc/ac converter.

60° of the line cycle. In sectors PI and PIV,  $|v_{CA}|$  is synthesized on the PDCL waveform using two sets of pulses synthesized by  $|v_{AB}|$  and  $|v_{BC}|$  as the voltage reference signals. These two sets of pulses are generated by the two-full-bridge modules of the dc/ac converter. In sectors PII and PV,  $|v_{AB}|$  is synthesized on the PDCL waveform using  $|v_{BC}|$  and  $|v_{CA}|$  as the voltage reference signals of the full-bridge modules of the dc/ac converter. Finally, in sectors PIII and PVI,  $|v_{BC}|$  is synthesized using two sets of pulses synthesized by  $|v_{AB}|$  and  $|v_{CA}|$  as the voltage reference signals of the full-bridge modules of the dc/ac converter.

Equations (4)–(6) can be rewritten as

$$|v_{BC}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|)$$

$$0 < \omega t < \frac{\pi}{6} \text{ or for } \frac{\pi}{2} < \omega t < \frac{2\pi}{3}$$

(7)

$|v_{CA}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|)$

$$\frac{\pi}{6} < \omega t < \frac{\pi}{2} \text{ or for } \frac{5\pi}{6} < \omega t < \pi$$

(8)

$$|v_{AB}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|)$$

$$\frac{\pi}{6} < \omega t < \frac{\pi}{3} \text{ or for } \frac{2\pi}{3} < \omega t < \frac{5\pi}{6}.$$

(9)

Using (7)–(9), Modulator I of the dc/ac modulator can be implemented using the maximum and minimum signals of  $|v_{AB}|$ ,  $|v_{BC}|$ , and  $|v_{CA}|$ . This approach makes the implementation of the dc/ac modulator just based on the maximum and minimum function of the voltage reference signals.

For example, when  $\omega t$  is between 0 and  $\pi/6$ ,  $|v_{CA}|$  is the maximum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$  and  $|v_{AB}|$  is the minimum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ . Therefore, the voltage reference signal of Modulator I is  $|v_{CA}|$  minus  $|v_{AB}|$ , which is equal to  $|v_{BC}|$ . Modulator II uses  $|v_{AB}|$  (the minimum reference signal) as its voltage reference signal. Therefore, a set of pulses are synthesized by  $|v_{AB}|$  and the other set of the pulses are synthesized by  $|v_{BC}|$  on the PDCL waveform. Then, the average of two resulting consecutive pulses on the PDCL waveform over the switching cycle is equal to  $|v_{CA}|$  (the maximum reference signal). The duration of the synthesized zero states between these two sets of pulses on the PDCL waveform are calculated as follows:

$$z(t) = 1 - \max(|v_{AB}|, |v_{BC}|, |v_{CA}|).$$

(10)

These zero states on the PDCL waveform are used to achieve ZVS operation for the switches of the pulsating-dc/ac converter. Therefore,  $|v_{AB}|$  and  $|v_{BC}|$  are directly synthesized on the PDCL waveform by two full-bridge modules of the dc/ac converter. Also,  $|v_{CA}|$  is indirectly synthesized on the PDCL waveform as two consecutive pulses. Therefore, all the required voltage reference signals are synthesized on the PDCL waveform. As a result, two legs of the pulsating-dc/ac converter do not switch while the other leg switches at middle of the provided zero states on the PDCL waveform to achieve ZVS condition. The soft-switched HM scheme for the pulsating-dc/ac converter is explained in the following section.

As shown in Fig. 2, the HF carrier of Modulator I has 180° phase shift with respect to the HF carrier of Modulator II of the dc/ac converter. Therefore, the dc/ac converter generates a set of bipolar pulses at the end and beginning of the switching cycle. But, it also generates a set of bipolar pulses at the middle of the switching cycle. Consequently, two sets of the generated pulses by the full-bridge modules of the dc/ac converter have 180° phase shift with respect to each other.

Fig. 3 shows the HF carriers, references, signal-waveforms of Modulator I and Modulator II of the dc/ac converter, bipolar pulses for the HF transformers, and the resulting PDCL voltage waveform. As shown in Fig. 3, two sets of pulses with 180° phase shift are generated on the PDCL waveform with enough zero states to enable ZVS condition for the pulsating-dc/ac converter. As a result, the average of two consecutive pulses on the PDCL waveform over the switching cycle is equal to the maximum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ .

# *B.* Soft-Switched Hybrid Modulation for the Pulsating-DC/AC Converter

The modulation scheme to generate the required PDCL waveform for pulsating-dc/ac converter is described in the previous section. The two sets of generated pulses by the full-bridge modules of the dc/ac converter are used to decrease the switching requirement of the pulsating-dc/ac converter. Also, the zero

Fig. 9. Topological modes of the equivalent circuit shown in Fig. 7 to study the soft-switching operation of the pulsating-dc/ac converter.

| Frequency                 | Input<br>voltage                   | Output phase-to-<br>phase voltage | Output<br>power | Transformer<br>turns ratio |

|---------------------------|------------------------------------|-----------------------------------|-----------------|----------------------------|

| 21.6 kHz                  | 40 V                               | 208 V                             | 1 kW            | 1:4.2                      |

| Name                      | Components                         |                                   |                 |                            |

| dc/ac converter           | IRF3808; MOSFET, 75 V, 140 A, 7 mΩ |                                   |                 |                            |

| ac/pulsating-dc converter | D06S60; 600 V, 6A                  |                                   |                 |                            |

| pulsating-dc/ac converter | IPW60R045CP; 650V, 60A, 45 mΩ      |                                   |                 |                            |

| transformers              | Nano-crystalline core              |                                   |                 |                            |

TABLE I

Specifications and Main Components of the Implemented PDCL HF Inverter

states on the PDCL waveform are used to provide ZVS condition for the pulsating-dc/ac converter. The modulation scheme to generate switching signals for three legs of the pulsating-dc/ac converter is shown in Fig. 4. The sign of  $v_{AB}$  (as represented by  $\text{sgn}(v_{AB})$ ) is used to generate the complementary pulses for the second half of the line cycle. Each leg of the pulsating-dc/ac converter does not switch for two-thirds of the line cycle. For instance, the first leg of the pulsating-dc/ac converter operates only at HF when  $|v_{BC}|$  is greater than  $|v_{AB}|$  and  $|v_{CA}|$ . The available zero states on the PDCL waveform are calculated using (10). Therefore, the term z(t)/2 is added to the reference signals of the comparators to operate at middle of the zeros states on the PDCL waveform. As a result, the switches of the pulsating-dc/ac converter turn OFF/ON when the voltage across the PDCL waveform is zero. Fig. 5 shows a simplified operation overview of the softswitched HM. The dc/ac and pulsating-dc/ac modulators are respectively described in Figs. 3 and 4. A sine-wave rectifier is used to provide rectified sine-wave voltage reference signals  $(v_{AB}, v_{BC}, \text{ and } v_{CA})$  for the dc/ac and pulsating-dc/ac modulators. These modulators have synchronous carriers to achieve ZVS condition for the pulsating-dc/ac converter. The generated pulses for the pulsating-dc/ac converter are inverted when the sign of signal  $v_{AB}$  changes. Therefore, the sign of  $v_{AB}$  is provided for the pulsating-dc/ac modulator. The signals  $v_{AB}, v_{BC}$ , and  $v_{CA}$  are the output of the controller for close loop of the PDCL HF inverter.

Fig. 6 illustrates the switching scheme of the pulsating-dc/ac converter and the zero states on the PDCL over a line cycle. Fig. 6(b)-(d) shows the required gate signals to extract the

Fig. 10. Implemented prototype to validate the soft-switched hybrid modulation.

Fig. 11. Secondary-side voltage and current of a HF transformer of the PDCL HF inverter.

desired phase-to-phase output voltages using the soft-switched HM. The resulting output voltage  $v_{ba}$  is depicted in Fig. 6(e) before and after the output filter stage. Topological modes of operation are thoroughly presented in the next section.

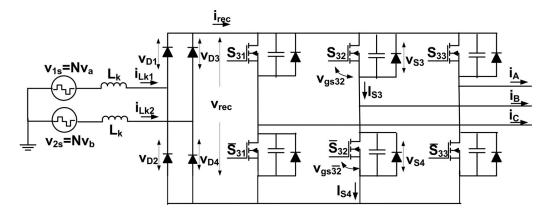

In order to study the topological modes of operation of the PDCL HF inverter using the soft-switch HM, an equivalent circuit is derived as shown in Fig. 7. It is obtained by eliminating the HF transformers and simplifying the dc/ac converter to ana-

Fig. 12. PDCL voltage and current waveform of the PDCL HF inverter using the soft-switched HM. Each switching cycle contains two pulses that represent different output sine-wave reference voltage signals as explained in Section II.

lyze the soft-switching operation of the soft-switched HM. The voltage supplies ( $v_{1s}$  and  $v_{2s}$ ) represent the secondary reflected voltages of transformers  $T_1$  and  $T_2$ , while the inductors are the secondary-side leakage inductances. The capacitors across the switches of the pulsating-dc/ac converter represent the parasitic capacitors of the switches.

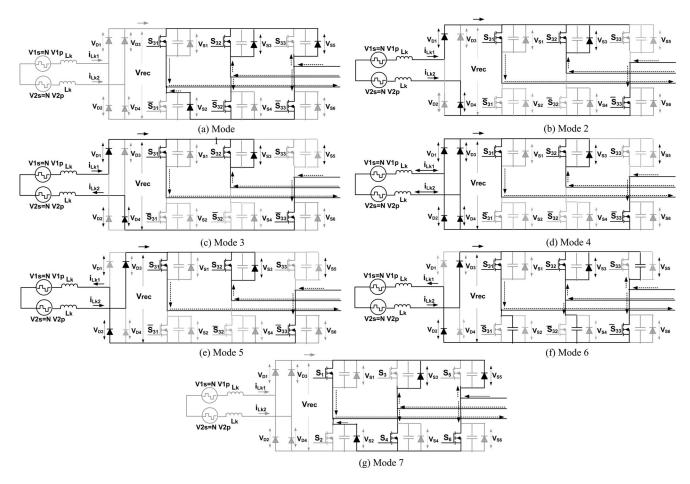

# III. MODES OF OPERATION

To analyze the modes of operation, the following assumptions are made:

- the voltage drops of the diodes and conduction losses of the switches are neglected;

- the dead time considered for the complementary switches of the pulsating-dc/ac converter is disregarded (it should be noted that switches of the pulsating-dc/ac converter operate at zero states, therefore; no dead time is necessary for complementary switches of the converter);

- the currents are considered to be constant during switching cycle;

- 4) the currents and voltages are assumed to be balanced threephase sinusoidal waveforms; that is

$$i_{A} = I_{m} \sin \left(\omega t + \gamma\right)$$

$$i_{B} = I_{m} \sin \left(\omega t + \gamma + \frac{2\pi}{3}\right)$$

$$i_{C} = I_{m} \sin \left(\omega t + \gamma + \frac{4\pi}{3}\right)$$

(11)

where  $I_m$  is the peak value of the line output currents and  $\gamma$  represents the power factor of the output load, which is negative for inductive load. A PDCL HF inverter with diode rectifier supports a power factor up to 30° according to [14]. Due to symmetry, the soft-switching operation of a leg of the pulsating-dc/ac converter is analyzed, which operates at HF.

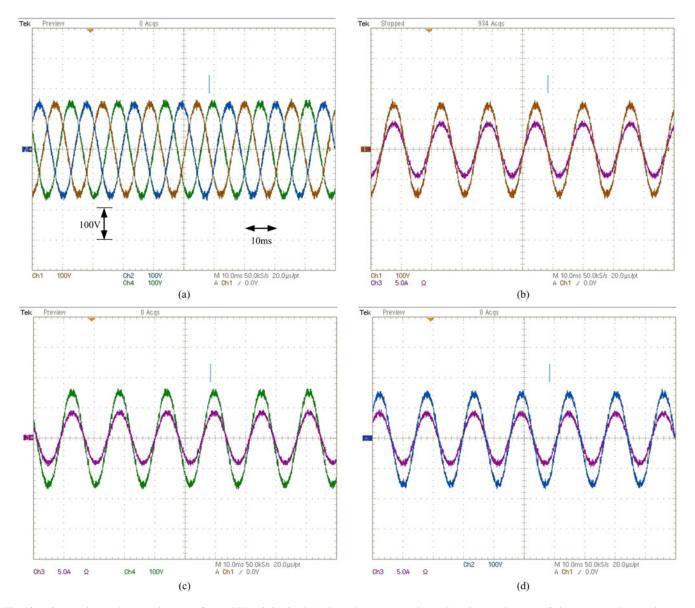

Fig. 13. Output phase voltages and currents for a 1-kW resistive load: (a) three-phase output voltage, (b) voltage and current of phase A, (c) voltage and current of phase B, and (d) voltage and current of phase C.

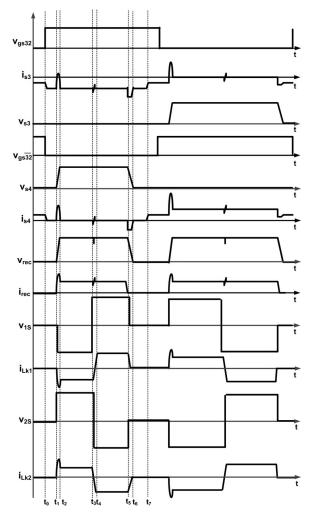

In this section,  $|v_{CA}|$  is greater than  $|v_{AB}|$  and  $|v_{BC}|$  and the sign of  $v_{AB}$  is negative. Therefore, switches  $S_{31}$ ,  $\bar{S}_{31}$ ,  $S_{33}$ , and  $\bar{S}_{33}$  do not switch. However, the second leg of the pulsating-dc/ac converter consisting of  $S_{32}$  and  $\bar{S}_{32}$  operates at HF. Currents  $i_A$  and  $i_C$  are positive, but  $i_B$  is negative. The topological modes of operation and the key waveforms are respectively shown in Figs. 8 and 9.

Mode 1 ( $t_0 < t < t_1$ ): Before  $t_0$ , $S_{32}$  is OFF and  $i_B$  is shared between  $\bar{S}_{32}$  and the body diode of  $S_{32}$ . Therefore, all the diodes of the ac/pulsating-dc converter are OFF and the currents freewheel in the legs of the pulsating-dc/ac converter. Therefore, the PDCL voltage  $v_{rec}$  and current  $i_{rec}$  are zero. Hence, the second leg ( $S_{32}$  and  $\bar{S}_{32}$ ) is switched under ZVS turn-on/off condition. This mode ends when  $v_{rec}$  starts to rise from zero.

*Mode 2*  $(t_1 < t < t_2)$ : At  $t = t_1$ , the voltage of the PDCL waveform starts to rise from zero. Before this instant, the voltage across parasitic capacitors of the switches is zero. Thus, D<sub>1</sub> and

Fig. 14. Output current THD versus output power of the inverter.

$D_4$  start to conduct to supply the required current for charging the parasitic capacitors of  $\bar{S}_{31}$ ,  $\bar{S}_{32}$ , and  $S_{33}$ .

Voltage supplies  $v_{1s}$  and  $v_{2s}$  are respectively equal to  $-NV_{in}$ and  $+NV_{in}$ . The current  $i_A$  is positive and  $S_{31}$  is ON. Consequently, the required current to charge the parasitic capacitor of

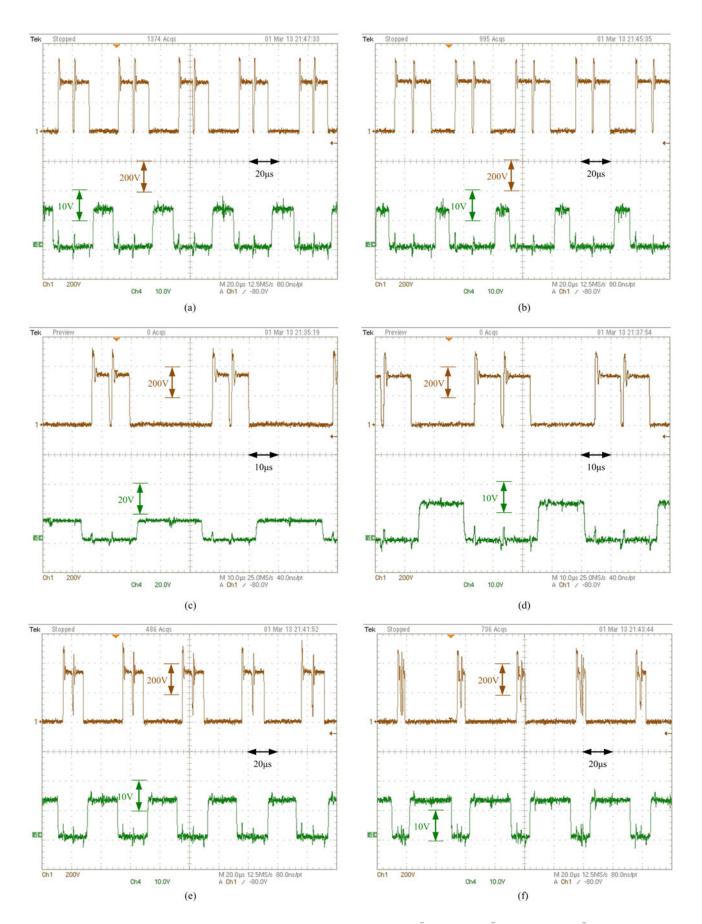

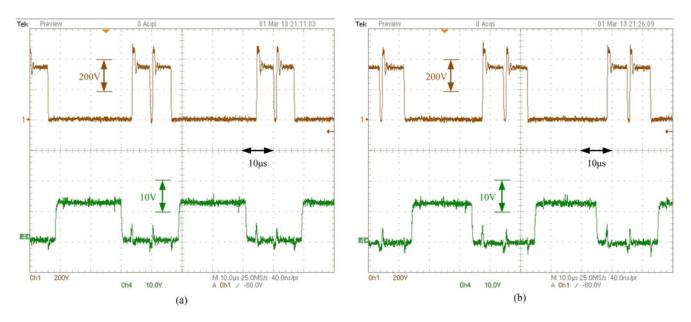

Fig. 15. Soft-switching operation of all switches of the pulsating-dc/ac converter: (a)  $S_{31}$ , (b)  $\bar{S}_{31}$ , (c)  $S_{32}$ , (d)  $\bar{S}_{32}$ , (e)  $S_{33}$ , and (f)  $\bar{S}_{33}$  (Ch1: drain-to-source voltage, and CH4: gate voltage).

Fig. 16. Output phase voltage and current of a phase of the PDCL HF inverter when it supplies an induction motor.

$\bar{S}_{31}$  is supplied by a path through  $S_{31}$ . The voltage across the parasitic capacitors is calculated as follows:

$$v_{s2} = v_{s4} = v_{s5} = v_c$$

2NV<sub>in</sub> =  $2L_k \frac{di_{Lk2}}{dt} + v_c$

$i_{c2} = i_{c4} = i_{c5} = C \frac{dv_c}{dt}.$  (12)

We can rewrite (10) as follows:

1:

$$2NV_{in} = 2L_k C \frac{d^2 v_c}{dt^2} + v_c.$$

(13)

According to (12), the resonant paths between the parasitic capacitors and the leakage inductances of the HF transformers build up the voltage of  $\bar{S}_{31}$ ,  $\bar{S}_{32}$ , and  $S_{33}$ . This mode ends at  $t = t_2$  when the voltage of the parasitic capacitors reaches their final value, which is equal to  $2NV_{in}$ .

*Mode 3* ( $t_2 < t < t_3$ ): At the beginning of this mode, the PDCL voltage waveform reached its final value. The currents are supplied by the PDCL. The current of the leakage inductances remains constant because their voltages are zero. At the end of this mode,  $v_{1S}$  and  $v_{2S}$  change their polarity.

*Mode 4* ( $t_3 < t < t_4$ ): In this mode,  $v_{1s}$  and  $v_{2s}$  are constant and respectively equal to NV<sub>in</sub> and –NV<sub>in</sub>. There are two commutations in the ac/pulsating-dc converter to change the current directions of the leakage inductances. As a result, D<sub>1</sub> commutes with D<sub>2</sub> and D<sub>3</sub> takes over the current of D<sub>4</sub>. The commutation times of the diodes are neglected here. Therefore, all the diodes conduct in this mode of operation. The leakage currents are taken over by D<sub>3</sub> and D<sub>2</sub> at the end of this mode. Therefore, the leakage inductance currents are equal and calculated as

$$2L_k \frac{dt_{Lk1}}{dt} = +2NV_{in}$$

$$i_{Lk1}(t) = i_{Lk1(t_3)} + \frac{NV_{in}}{L_k}(t - t_3).$$

(14)

Finally, the currents of leakage inductance are equal to the PDCL current.

*Mode 5* ( $t_4 < t < t_5$ ): This mode of operation starts when the currents of leakage inductances reached their final value to support the balanced output currents. Similar to Mode 3, the voltages across the leakage inductances are zero, consequently; the leakage currents are constant. At the end of this mode,  $v_{1s}$  and  $v_{2s}$  become zero and the leakage currents start to decrease.

Mode 6 ( $t_5 < t < t_6$ ): The PDCL voltage waveform tends to decrease, because the secondary winding voltages are zero. As a result, the body capacitors of  $\overline{S}_{31}$ ,  $\overline{S}_{32}$ , and  $S_{33}$  are being discharged by output load currents. This mode ends when the leakage currents become zero and load currents start to freewheel again in the pulsating-dc/ac converter. In this mode of operation,  $S_{32}$  turns OFF under zero voltage turn-off condition because the voltage of the PDCL waveform is zero.

Mode 7 ( $t_6 < t < t_7$ ):  $\bar{S}_{32}$  is OFF and  $i_B$  must pass through the  $S_{32}$  and its body diode.  $\bar{S}_{32}$  turns ON under zero-voltage turn-on condition. Similar to Mode 1, the load current shares between  $S_{32}$  and  $\bar{S}_{32}$ . Therefore, the load currents again freewheel in the pulsating-dc/ac converter. The ZVS operation of the other switches has the same principle of operation during other operation conditions.

# IV. EXPERIMENTAL RESULTS

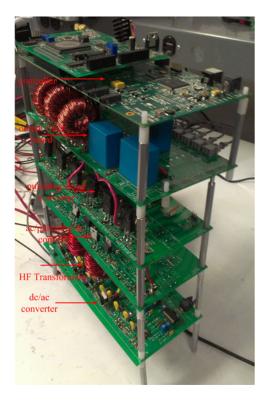

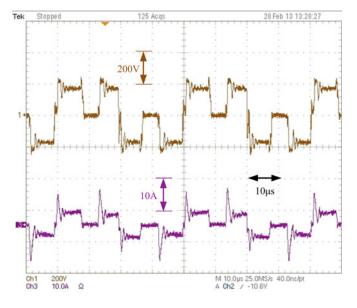

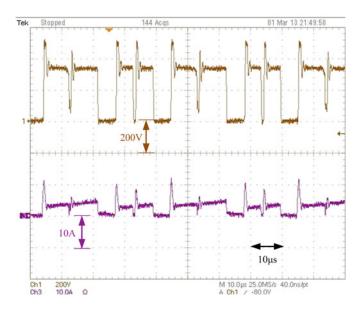

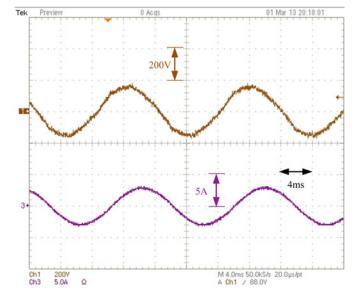

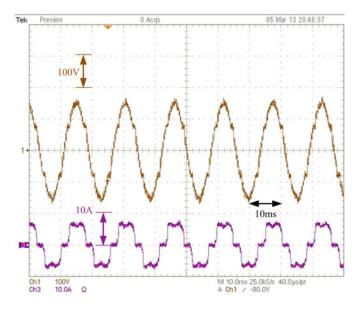

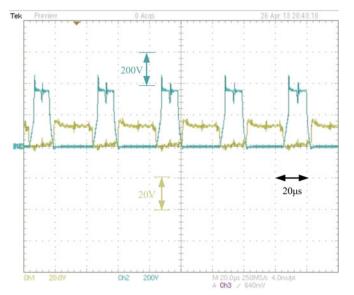

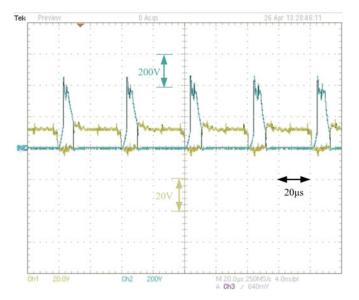

The specifications and main components of the implemented PDCL HF inverter for validating the operation of the softswitched HM scheme are summarized in Table I. Fig. 10 shows the implemented prototype of the PDCL HF inverter to validate the soft-switched HM. The output filter capacitors and inductors are respectively 5  $\mu$ F and 1 mH. The secondary-side voltage and current of a HF transformer of the PDCL HF inverter are shown in Fig. 11. The secondary-side voltage waveforms of the HF transformers are rectified by the ac/pulsating-dc converter to generate the PDCL waveform. The Fig. 12 shows the resulting PDCL waveform using the explained modulation scheme in Section II for the dc/ac converter. The resulting zero states on the PDCL waveform provide ZVS turn-on/off condition for the pulsating-dc/ac converter. These two pulses with different widths are related to different output sine-wave reference voltage signals.

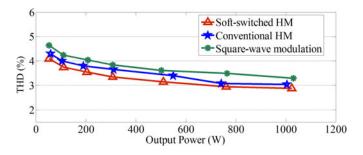

Fig. 13(a) shows the three-phase output sine-wave voltages using soft-switched HM modulation for a 1 kW resistive load. The respective output phase voltages and currents of the PDCL HF inverter are shown in Figs. 13(b)–(d). The THD of the HF PDCL inverter for the soft-switched HM, the conventional HM, and square-wave modulation is shown in Fig. 14. The soft-switched HM shows a more promising THD because of soft-switching of the pulsating-dc/ac converter. The resulting THD of the PDCL HF inverter is well below 5% for a wide range of the output powers for the soft-switched HM.

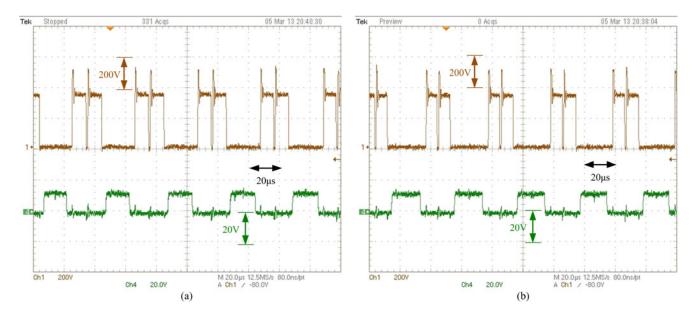

The ZVS soft-switching operation of the pulsating-dc/ac converter is shown in Fig. 15. All of the switches turn ON/OFF in the zero states available on the PDCL voltage waveform. The ZVS operation and performance of the PDCL HF inverter using soft-switched HM scheme is evaluated when the inverter

Fig. 17. Soft-switching operation of the first leg of the pulsating-dc/ac converter when it supplies an induction load: (a)  $S_{31}$ , (b)  $\bar{S}_{31}$  (Ch1: drain to source voltage, and CH4: gate voltage).

supplies an induction motor. The power factor of the motor is about 30°. The obtained output voltage and current of a phase of the PDCL HF inverter is shown in Fig. 16. The THD of the output voltage of the inverter is 4.7% for this inductive load. Fig. 17 shows the ZVS operation of the PDCL HF inverter for the first leg of the pulsating-dc/ac converter when the PDCL HF inverter supplies the induction motor. A three-phase diode rectifier is used as a nonlinear load for the implemented PDCL HF inverter. Fig 18 shows the output voltage and current waveforms of the inverter when it supplies a nonlinear load. The THD of the output voltage is 4.85% when the output power is 1 kW. The soft-switching operation of the inverter for the first leg of the inverter is shown in Fig. 19.

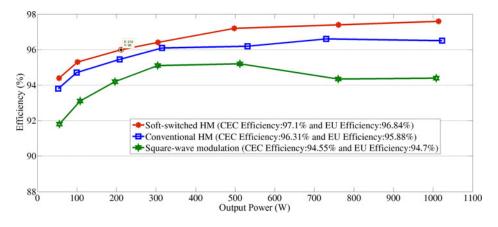

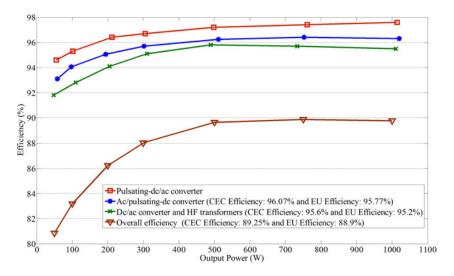

The efficiency of the soft-switched HM scheme, the conventional HM, and the square-wave modulation scheme in [9] for PDCL HF inverters are compared using the implemented inverter. The achieved efficiencies for the PDCL HF inverter using the mentioned schemes are shown in Fig. 20. The efficiency of the pulsating-dc/ac converter is increased using the soft-switched HM compared to other modulation schemes. The efficiency of the three stage of the PDCL HF inverter is depicted in Fig. 21. The conduction loss of the dc/ac converter is dominant because of high current rating of the front-end stage. However, the ac/pulsating-dc and pulsating-dc/ac converters have considerably lower conduction loss. Therefore, switching loss is dominant at the stages after the secondaryside of the HF transformers. European weighted efficiency and The California Energy Commission (CEC) weighted efficiencies are calculated and recorded in Figs. 21 and 22.

The operation of the soft-switched HM is reviewed for the light load conditions. As explained in Section III, load currents charge and discharge the parasitic capacitors of the switches of the pulsating-dc/ac converter. Therefore, enough load currents is required to provide the zero states for the ZVS operation of

Fig. 18. Output voltage and current of a phase of the PDCL HF inverter when it supplies a nonlinear load.

the pulsating-dc/ac converter. Fig. 22 shows the soft-switching operation of switch  $S_{31}$  when the output power is 50 W. Because parasitic capacitors of the switches are typically small (320 pF for IPW60R045CP MosFets), enough zero states are generated on the PDCL waveform. Therefore, the soft switching is achieved for light load although it takes more time to discharge the parasitic capacitors. The Fig. 23 shows the drain– source voltage and the gate signal of switch  $S_{31}$  when the output power is 40 W. The ZVS operation is lost due to lack of enough load currents. But, the switch still commutate at lower voltages compared to the conventional HM.

Fig. 19. Soft-switching operation of the first leg of the pulsating-dc/ac converter when it supplies a nonlinear load: (a)  $S_{31}$ , (b)  $\bar{S}_{31}$  (Ch1: drain to source voltage, and CH4: gate voltage).

Fig. 20. Efficiency of the pulsating-dc/ac converter.

Fig. 21. Efficiency of the different stages of the PDCL HF inverter.

Fig. 22. Soft-switching operation of  $S_{31}$ .

Fig. 23. Operation of the  $S_{31}$  when the output power is 40 W.

#### V. CONCLUSION

Lossless mitigation of the pulsating-dc/ac converter is achieved using the soft-switched hybrid modulation due to switching transition during the zero states. The pulsating-dc link waveform has two different phase-to-phase representations that lead to soft-switching operation of the pulsating-dc/ac converter. The soft-switching operation of the pulsating-dc/ac converter can be extended to the ac/pulsating-dc converter when full controlled switches are used for the ac/pulsating-dc/ac converter. The soft-switching operation of the pulsating-dc/ac converter is independent of the load type. Its operation is validated for resistive, inductive, and nonlinear loads.

#### VI. DISCLAIMER

The hybrid modulation mechanism outlined in this paper is covered by the following patent:

S.K. Mazumder and R. Huang, "Multiphase converter apparatus and method," USPTO Patent# 7,768,800 B2, awarded on August 3, 2010.

#### REFERENCES

- M. Matsui, T. Kitano, S. Ohba, and D. Xu, "New space vector modulation scheme based high-frequency link soft-switching converter for AC system line interface," in *Proc. Power Convers. Conf.*, Osaka, 2002, pp. 478–485.

- [2] K. Wang, F. C. Lee, and W. Dong, "A new soft-switched quasi-singlestage (QSS) bi-directional inverter/charger," in *Proc. IEEE Ind. Appl. Soc. Annu. Meet.*, 1999, pp. 2031–2038.

- [3] A. M. Hava and E. Un, "A high-performance PWM algorithm for common-mode voltage reduction in three-phase voltage source inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1998–2008, Jul. 2011.

- [4] A. M. Hava and N. O. Cetin, "A generalized scalar PWM approach with easy implementation features for three-phase, three-wire voltage-source inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1385–1395, May 2011.

- [5] H. Cha and P. N. Enjeti, "A new soft switching direct converter for residential fuel cell power system," in *Proc. IEEE Ind. Appl. Soc. Annu. Meet.*, 2004, pp. 1172–1177.

- [6] W. Yunxiang, M. A. Shafi, A. M. Knight, and R. A. McMahon, "Comparison of the effects of continuous and discontinuous PWM schemes on power losses of voltage-sourced inverters for induction motor drives," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 182–191, Jan. 2011.

- [7] E. Koutroulis, J. Chatzakis, K. Kalaitzakis, and N. C. Voulgaris, "Bidirectional, sinusoidal, high-frequency inverter design," in *Proc. Inst. Electr. Eng. Electr. Power Appl.*, Jul. 2001, vol. 148, no. 4, pp. 315–321.

- [8] R. Li, Z. Ma, and D. Xu, "A ZVS grid-connected three-phase inverter," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3595–3604, Aug. 2012.

- [9] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

- [10] X. Yaosuo, C. Liuchen, S. B. Kjaer, J. Bordonau, and T. Shimizu, "Topologies of single-phase inverters for small distributed power generators: an overview," *IEEE Trans. Power Electron.*, vol. 19, no. 5, pp. 1305–1314, Sep. 2004.

- [11] N. Henze, B. Sahan, R. Burger, and W. Belschner, "A novel ac module with high-voltage panels in CIS technology," *Eur. PV Solar Energy Conf. Exhib.*, Spain, Sep. 2008.

- [12] Z. Yan, M. Jia, C. Zhang, and W. Wu, "An integration SPWM strategy for high-frequency link matrix converter with adaptive commutation in one step based on de-re-coupling idea," *IEEE Trans. Ind. Electron*, vol. 59, no. 1, pp. 116–128, Jan. 2012.

- [13] A. Schönung and H. Stemmler, "Static frequency changers with subharmonic control in conjunction with reversible variable speed ac drives," *Brown Boveri Rev.*, vol. 51, pp. 555–577, 1964.

- [14] K. W. Leen and F. C. Lai, "Operation principles of bi-directional fullbridge dc/pulsating-dc converter with unified soft-switching scheme and soft-starting capability," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2000, pp. 111–118.

- [15] C. B. Jacobina, A. M. Lima, and E. R. da Silva, "Digital scalar pulse-width modulation: A simple approach to introduce non-sinusoidal modulating waveforms," *IEEE Trans. Power Electron.*, vol. 16, no. 3, pp. 351–359, May 2001.

- [16] D. G. Holmes and T. A. Lipo, Pulse-Width Modulation for Power Converters: Principles and Practice. Hoboken, NJ, USA: Wiley, 2003.

- [17] L. Dalessandro, S. D. Round, U. Drofenik, and J. W. Kolar, "Discontinuous space-vector modulation for three-level PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 530–542, Mar. 2008.

- [18] O. Ojo, "The generalized discontinuous PWM scheme for three-phase voltage source inverters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 6, pp. 1280– 1289, Nov./Dec. 2004.

- [19] D. Zhang, F. Wang, R. Burgos, and D. Boroyevich, "Common-mode circulating current control of paralleled interleaved three phase two-level voltage-source converters with discontinuous space-vector modulation," *IEEE Trans. Power Electron.*, vol. 26, no. 12, pp. 3925–3935, Dec. 2011.

- [20] R. Huang and S. K. Mazumder, "A soft-switching scheme for an isolated dc/pulsating-dc converter with pulsating dc output for a three-phase highfrequency-link PWM converter," *IEEE Trans. Power Electron.*, vol. 24, no. 10, pp. 2276–2288, 2009.

- [21] S. K. Mazumder and R. Huang, "Multiphase converter apparatus and method," USPTO Patent# 7 768 800 B2, Aug. 2010.

- [22] S. K. Mazumder, "A novel hybrid modulation scheme for an isolated high-frequency-link fuel cell inverter," in *Proc. IEEE Power Energy Soc. General Meet. – Convers. Del. Electr. Energy 21st Century*, 2008, pp. 1–7.

- [23] A. Rahnamaee, S. K. Mazumder, and A. Tajfar, "A novel modulationbased zero-voltage and zero-current switched high-frequency-link inverter for renewable-energy systems," in *Proc. IEEE Power Electron. Spec. Conf.*, 2011, pp. 784–790.

- [24] S. J. Finney, B. W. Williams, and T. C. Green, "RCD snubber revisited," *IEEE Trans. Ind. Appl.*, vol. 32, no. 1, pp. 155–160, Jan./Feb. 1996.

Arash Rahnamaee (S'08) received the B.S. degree in electrical power engineering from the University of Tabriz, Tabriz, Iran, and the M.S. degree in electrical power engineering from Amirkabir University of Technology (Tehran Polytechnic), Tehran, Iran. He is currently working toward the Ph.D. degree at the Laboratory for Energy and Switching-Electronics System, University of Illinois at Chicago, Chicago, IL, USA.

He has authored and coauthored more than ten published journal and conference papers. His current

research interests include power electronics for renewable energy sources, energy harvesting, motor drives, and electric vehicles.

Mr. Rahnamaee is a Reviewer for the IEEE TRANSACTIONS ON POWER ELECTRONICS and the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

Sudip K. Mazumder (S'97–M'01–SM'03) received the M.S. degree in electrical power engineering from Rensselaer Polytechnic Institute, Troy, NY, USA, in 1993, and the Ph.D. degree in electrical and computer engineering from the Virginia Polytechnic Institute and State University (VPI&SU), Blacksburg, VA, USA, in 2001.

He is currently the Director of Laboratory for Energy and Switching-Electronics Systems and a Professor in the Department of Electrical and Computer Engineering, University of Illinois, Chicago,

IL, USA. He has more than 20 years of professional experience and has held R&D and design positions in leading industrial organizations and has served as technical consultant for several industries. He also serves as the President of NextWatt LLC, a small business organization that he setup in 2008. Since joining UIC, he has been awarded close to 40 sponsored projects by NSF, DOE, ONR, CEC, EPA, AFRL, NASA, ARPA-E, NAVSEA, and multiple leading industries in abovereferenced areas. He has published more than 150 refereed papers in prestigious journals and conferences and has published one book and six book chapters. Twenty four of his journal papers are published in IEEE transactions with a current impact factor >4. He has presented 43 invited/plenary/keynote presentations and currently, he also holds six issued and three pending patents.

Dr. Mazumder received the University of Illinois's University Scholar Award in 2013. In 2011, he received the Teaching Recognition Program (TRP) Award at UIC. In 2008 and 2006, he received the prestigious Faculty Research Award from the UIC for outstanding research performance and excellent scholarly activities. He also received the ONR Young Investigator Award and the NSF CAREER Awards in 2005 and 2003, respectively, and the prestigious IEEE Prize Paper Awards in 2002 and 2007, respectively. He also received the best paper presentation in a session award certificate from the IEEE Industrial Electronics Conference in 2004 and 2012. In 2005, he led a team of the University of Illinois, Chicago student team to first place in USA and third place in the world as a part of the highly reputed IEEE sponsored International Future Energy Challenge competition. He served as the first Editor-in-Chief for the International Journal of Power Management Electronics (currently known as Advances in Power Electronics) between 2006 and 2009. He has also served or is serving as a Guest Editor/Guest Co-Editor for the following transaction special issues: IEEE TRANSACTIONS ON POWER ELECTRONICS SPECIAL ISSUE ON POWER ELECTRONICS IN DC DISTRIBUTION SYSTEMS (2011–2013); ADVANCES IN POWER ELECTRONICS SPECIAL ISSUE ON Advances in Power Electronics for Renewable Energy (2010-2011); IEEE TRANSACTIONS ON POWER ELECTRONICS SPECIAL ISSUE ON HIGH-FREQUENCY-LINK POWER-CONVERSION SYSTEMS (2013-2014); IEEE TRANS-ACTIONS ON INDUSTRIAL ELECTRONICS SPECIAL ISSUE ON CONTROL STRATE-GIES FOR SPATIALLY DISTRIBUTED INTERACTIVE POWER NETWORKS (2013-2014) (in process for submission); and Advances in Power Electronics Special Issue on All Electric Ship Technology (2012-2013). Currently, he serves as an Associate Editor for the following transactions: IEEE TRANSACTIONS ON POWER ELECTRONICS (since 2009), IEEE TRANSACTIONS ON INDUSTRIAL ELECTRON-ICS (since 2003), and IEEE TRANSACTIONS ON AEROSPACE AND ELECTRONICS SYSTEMS (since 2008). He is also an Editorial Board Member for the Advances in Power Electronics. Previously, he has also served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS and the IEEE POWER ELECTRONICS LETTER. In 2010, he served as the Chair, Student/Industry Coordination Activities for IEEE Energy Conversion Congress and exposition, which is the largest conference in power electronics today in North America. He served as the Cochair for the IEEE Power Electronics Society (PELS) Technical Committee on Sustainable Energy Systems and is currently serving as the Vice Chair of the IEEE PELS Subcommittee on Distributed Generation and Renewable Energy. He is also serving as the Advisory Committee Member for the 2012 IEEE India International Conference on Power Electronics and has also served in the same capacity for the 2010 IEEE International Symposium on Power Electronics for Distributed Generation Systems. He is serving/has served as a Technical Program Committee Member for numerous IEEE sponsored and other reputed conferences including the IEEE Energy Conversion Congress and Exposition, the IEEE Applied Power Electronics Conference and Exposition, the IEEE Industrial Electronics Conference, the IEEE International Symposium on Power Electronics for Distributed Generation Systems. He was invited by the inaugural 2012 Clean Energy Trust Show Case, an event that connected entrepreneurs, investors, and researchers who can work together to commercialize the latest clean technology, to deliver his vision on Smart Grid.