AQ:1

# Overview of Wide/Ultrawide Bandgap Power Semiconductor Devices for Distributed Energy Resources

Sudip K. Mazumder<sup>®</sup>, Fellow, IEEE, Lars F. Voss<sup>®</sup>, Karen M. Dowling<sup>®</sup>, Member, IEEE, Adam Conway, David Hall, Robert J. Kaplar<sup>®</sup>, Senior Member, IEEE, Gregory W. Pickrell<sup>®</sup>, Senior Member, IEEE, Jack Flicker<sup>®</sup>, Senior Member, IEEE, Andrew T. Binder, Srabanti Chowdhury<sup>®</sup>, Senior Member, IEEE, Victor Veliadis, Fellow, IEEE, Fang Luo<sup>®</sup>, Senior Member, IEEE, Sameh Khalil, Thomas Aichinger, Sandeep R. Bahl, Senior Member, IEEE, Matteo Meneghini, Senior Member, IEEE, and Alain B. Charles

AQ:2

AO:3

Abstract— This article provides an overview of power semiconductor devices (PSDs) for the distributed energy resource (DER) system. To begin with, an overview of electrically triggered SiC and gallium nitride (GaN) devices followed by a brief narration of ultrawide bandgap (UWBG) PSDs and, subsequently, an overview of optically activated PSDs encompassing photoconductive semiconductor switch (PCSS) and optical bipolar PSDs are provided. Finally, an overview of PSD packaging and reliability is captured.

Index Terms—Devices, electrical, materials, optical, packaging, reliability, ultrawide bandgap (UWBG), wide bandgap (WBG).

I. INTRODUCTION

DISTRIBUTED energy resource (DER) is any resource in the distribution system that produces electricity and is not otherwise included in the formal North American Electric Reliability Corporation (NERC) definition of the bulk electric system (BES) [1]. DERs include any non-BES resource located solely within the boundary of any distribution utility and distribution provider, including the following: distributed

AQ:5

12

13

15

AQ:6 AQ:7

AQ:8 AQ:9 AQ:10 Manuscript received 15 January 2023; revised 3 April 2023 and 2 May 2023; accepted 4 May 2023. Recommended for publication by Associate Editor Xu She. (Corresponding author: Sudip K. Mazumder.)

Sudip K. Mazumder is with the University of Illinois Chicago, Chicago, IL 60607 USA (e-mail: mazumder@uic.edu).

Lars F. Voss is with the Lawrence Livermore National Laboratory, Livermore, CA 94550 USA.

Karen M. Dowling is with the Delft University of Technology (TU Delft), 2628 CD Delft, The Netherlands.

Adam Conway is with Raytheon Technologies, USA.

David Hall is with II-VI.

Robert J. Kaplar, Gregory W. Pickrell, Jack Flicker, and Andrew T. Binder are with the Sandia National Laboratories, Albuquerque, NM USA.

Srabanti Chowdhury is with Stanford University, Stanford, CA 94305 USA. Victor Veliadis is with North Carolina State University, Raleigh, NC 27695 USA.

Fang Luo is with Stony Brook University, Stony Brook, NY 11794 USA. Sameh Khalil is with Infineon.

Thomas Aichinger is with Infineon Technologies, El Segundo, CA, USA. Sandeep R. Bahl is with Texas Instruments, Dallas, TX USA.

Matteo Meneghini is with the University of Padua, 35122 Padua, Italy. Alain B. Charles is with ABCsWorld Consulting, Redondo Beach, CA USA. Color versions of one or more figures in this article are available at https://doi.org/10.1109/JESTPE.2023.3277828.

Digital Object Identifier 10.1109/JESTPE.2023.3277828

generation, behind-the-meter generation, energy storage facility, DER aggregation, microgrid, virtual power plant, cogeneration, and emergency/standby/back-up generation [1]. The power and voltage ranges for the DERs vary considerably ranging from below 1 to below 69 kV and a few kilowatts to several megawatts. As such, the power semiconductor devices (PSDs) that serve as the actuators for the DER power electronics need to encompass a wide range of voltage and power levels. Conventional silicon (Si) power devices have dominated DER power electronics due to their low cost, excellent starting material quality, ease of processing, good performance with low loss, and proven reliability. Recently, PSDs based on wide bandgap (WBG) semiconductors [e.g., SiC and gallium nitride (GaN)] and ultrawide bandgap (UWBG) semiconductors (e.g., Ga<sub>2</sub>O<sub>3</sub>, diamond, and nitrides), as outlined in Sections II and III, are also emerging that evince potential for efficient PSDs for medium- and high-voltage DERs.

21

23

34

36

42

49

51

53

57

The main advantages of WBG and UWBG devices are the increase in blocking voltage and the enabling of highfrequency switching, which they are capable of relative to traditional Si devices. High-voltage blocking directly enables higher voltage operation of the power conversion system and could enable simple topologies to be utilized for MV applications that now require either modular, multilevel converters or single-stage converters with serially connected switches. This simpler topology would enable cost reduction in MV power conversion and increased reliability due to a lower component count. In addition, the use of WBG and UWBG devices enables the operation of the system at higher switching speeds. This has a twofold benefit. The first is a reduced requirement for passive energy storage components. This reduces the size, weight, and cost of the power converter with applications, including, but not limited to, solid-state transformer, integration wind-cycloconverter system, and high-frequency-link power conversion. This can introduce significant benefits in the balance of system cost due to savings in shipping the unit and the installation, especially if this can be done without the use of a crane or other machinery. The higher switching frequency also enables higher control bandwidth in the system, which can enable new forms of system-level control. Since the

transient response of the power electronic system is determined via controls and not physics (as in a traditional rotating machine), new modes of operation are enabled through nearly arbitrary subtransient response. This can have outsized benefits to system contingency by, for example, allowing the DER to replicate the inertia of a rotating mass in a contingency event.

Furthermore, while the traditional approach to the realization of such PSDs for DERs has been based dominantly on electrical triggering, new research has begun to show the potential of optical triggering in PSDs. This is captured in Section IV, including the benefits of low latency, rapid switching, immunity to electromagnetic interference (EMI) noise, and uniformity of device triggering for high-voltage scaling without incurring complexities of floating gate drivers. In addition, other emerging applications leveraging the ultrafast performance of optical PSDs, such as GaN photoconductive semiconductor switch (PCSS) operating in the nonlinear mode, are being investigated for rapid fault isolation.

Yet another issue pertains to packaging, as detailed in Section V. WBG semiconductors (SiC and GaN) due to their enhanced performance and superior material properties compared to traditional Si power devices have become the ultimate choice for future high-performance energy conversion. Since traditional device packaging becomes a limiting factor in fully harnessing the benefits offered by the advanced PSDs, improved and advanced packaging structures are necessary to bridge the gap between WBG devices and their applications [2], [3], [4], [5], [6].

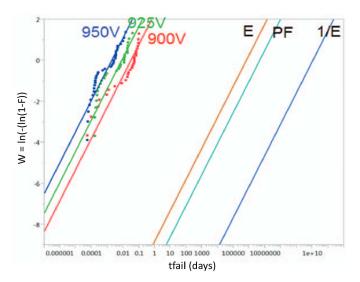

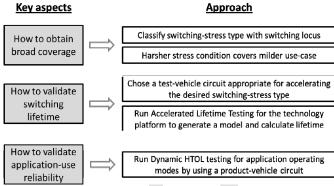

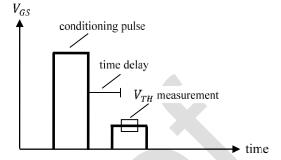

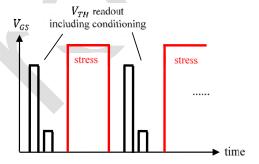

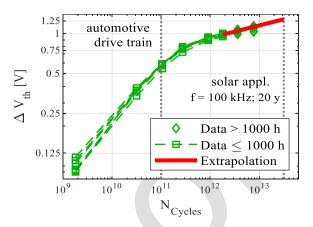

A final issue, as outlined in Section VI, relates to the reliability of the PSDs. Methodologies to ensure reliable WBG products were proposed and reported in the literature [7] and discussed in WBG and reliability conferences and workshops. For GaN-based power devices, time-dependent-dielectric-like breakdown, dynamic ON-state resistance due to trapping effects, and hard switching are among the key topics that are currently in focus by the research and development community. A significant knowledge base has been accumulated since 2005. For SiC-based power devices, power cycling, humidity robustness, bipolar degradation, gate oxide reliability, and bias temperature instabilities are among the hot topics. Test and screening procedures need to be adapted and extended to account for different material properties, higher fields, crystal defects, and a more complex MOS system.

# II. WBG Power Semiconductor Devices

#### A. SiC Devices

WBG PSDs are currently in production for high-power/temperature applications. SiC is ideally suited for power switching due to its high saturated drift velocity, its large bandgap, its excellent thermal conductivity, and its high critical field strength. For power devices, the tenfold increase in critical field strength of SiC relative to Si allows high-voltage blocking layers to be fabricated significantly thinner than those of comparable Si devices. This reduces device ON-state resistance, and the associated conduction and switching losses while maintaining the same high-voltage blocking capability. Lower switching losses allow for high-frequency operation,

| Properties                                                                           | Materials |          |         |

|--------------------------------------------------------------------------------------|-----------|----------|---------|

|                                                                                      | Si        | SiC (4H) | GaN     |

| Electric breakdown field (MV cm <sup>-1</sup> )                                      | 0.3       | 2.2      | 3.3     |

| Energy gap (eV)                                                                      | 1.12      | 3.26     | 3.39    |

| Saturated electron velocity (x 10 <sup>7</sup> cm s <sup>-1</sup> )                  | 1         | 2        | 2.5     |

| Electron mobility (x 10 <sup>3</sup> cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | 1.4       | 0.95     | 0.8-1.7 |

| Thermal conductivity (W cm <sup>-1</sup> K <sup>-1</sup> )                           | 1.5       | 4.5      | 4       |

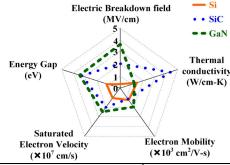

Fig. 1. Graphical comparison of Si, SiC, and GaN material properties.

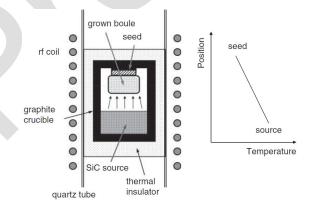

Fig. 2. Schematic description of crucible for seeded sublimation growth of SiC substrates.

which minimizes the size and weight of a system's passive components. The low specific ON-state resistance enables high-current operation at a relatively low forward voltage drop at a given breakdown voltage. Also, the WBG of SiC allows operation at high temperatures, where conventional Si devices fail, with low leakage and reduced cooling system requirements. A graphical summary of Si-, SiC-, and GaN-relevant material properties is shown in Fig. 1 [6].

To exploit SiC's compelling material properties in power devices, significant efforts started in the 1980 s to develop high-quality low defect SiC substrates and epitaxy. Today, 150-mm SiC wafers are primarily used in the production of SiC devices. 200-mm wafers were demonstrated in 2015 and are expected to become commercially available shortly. It should be noted that conventional SiC substrate growth is more complex than that of Si requiring the use of large seeds and high process temperatures. SiC is mainly grown by the seeded sublimation technique, as schematically shown in Fig. 2.

The raw material, SiC powder, is placed at the bottom of a graphite crucible. A seed wafer is placed at the top of the crucible, which is heated by RF coils to a temperature of  $\sim 2500$  °C. The seed wafer is kept at a lower temperature than

183

184

186

188

190

191

192

194

195

197

198

199

200

201

203

205

206

207

210

211

212

214

216

218

220

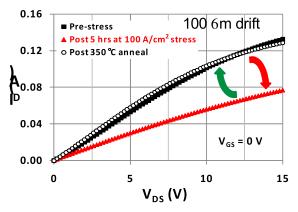

Fig. 3. BPD-related JFET ON-state degradation and recovery by annealing at 25  $^{\circ}$ C

140

141

143

145

147

149

150

151

152

153

154

155

156

157

158

160

161

162

163

164

165

166

167

168

169

170

171

173

175

177

178

179

the SiC powder, and the sublimed SiC species condensate and crystallize on the seed wafer. Reported sublimation growth rates are in the order of 0.5–2 mm/h. Increasing the growth rate can have the undesirable side effect of increased structural defect inclusion in the boule. SiC material's hardness, which is comparable to that of diamond, makes sawing and polishing SiC substrates slow and costly relative to Si. The epitaxial active SiC device layer is grown by chemical vapor deposition (CVD) in horizontal or planetary reactors at about 1550 °C. The epitaxial growth is done on 4° off-cut substrates to maintain the polytype stability of the substrate. SiC epitaxial growth is well established and strives to minimize defect propagation from the substrate to the epitaxial layer.

Historically, killer defects limiting yield have been polytype inclusions and micropipes. These have been practically eliminated in commercial wafers. Micropipe density, which is detrimental to device operation, is typically below 0.1 cm<sup>-2</sup>. The remaining structural defects are threading screw dislocations (300-600 cm<sup>-2</sup>) that can increase reverse voltage leakage, threading edge dislocations (2000–5000 cm<sup>-2</sup>) that are considered benign, and basal plane dislocations (BPDs) (500-3000 cm<sup>-2</sup>), which leads to device degradation under bipolar current flow. Although threading dislocations do result in measurable disturbances of epitaxial layer surface morphology, the practical effects of these disturbances on device performance and reliability are minimal [8]. BPDs are the major remaining "killer" defect impacting bipolar SiC devices and unipolar devices that conduct bipolar current during their operational cycle [9]. BPDs can be present in the starting SiC wafer and can also be generated during the high-temperature ion-implantation process. Interestingly, transistor BPD-related electrical characteristics degradations can be fully reversed by annealing at 350 °C, while nondegraded characteristics remain unaffected by the annealing (see Fig. 3) [10].

Numerous well-established processes from Si technology have been successfully transferred to SiC. However, SiC material properties necessitate the development of specific processes, whose parameters must be optimized and qualified. SiC is inert against chemical solvents, and only dry etching is practical. Conventional thermal diffusion is not realistic in doping SiC due to its high melting point and the low diffusion constant of dopants within SiC; heated ion implantation must

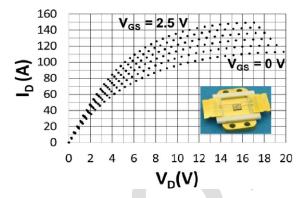

Fig. 4. ON-state drain current versus voltage characteristics of a single 1680-V, 0.143-cm<sup>2</sup> packaged JFET at a gate bias range of 0–2.5 V in steps of 0.5 V at a temperature of 25 °C.

be performed followed by a 1600 °C-1800 °C anneal for SiC recrystallization and implant activation. The high value of the SiC/metal barrier results in rectifying metal contacts. Post-metal deposition anneal is required for ohmic contact formation. Unlike Si wafers, those of SiC are transparent. This complicates critical dimension scanning electron microscope (CD-SEM) and metrology measurements as the focal plane is determined with the use of an optical microscope. SiC-specific metrology/inspection tools are now becoming available from multiple vendors. The relative lack of flatness of SiC wafers, compared to that of Si, can complicate photolithography and other processing particularly as high-temperature processes can further degrade wafer flatness rendering wafers unusable. Finally, the poor SiC/SiO<sub>2</sub> interface quality reduces inversion layer mobility, and passivation techniques are utilized to improve the SiC/SiO<sub>2</sub> interface quality. SiC process integration technology has made significant advancements, and optimizations are continuing. Today, SiC diodes and transistors are commercially available from multiple vendors.

To effectively compete with Si, large-area reliable and rugged SiC devices must be produced at a competitive cost. Early proof-of-concept work paved the way for investments that contributed to SiC commercialization. In 2008, a 1680-V SiC JFET with an active area of 0.143 cm<sup>2</sup> and an ON-state current capability of 50 A was the largest transistor reported to date (see Fig. 4) [11].

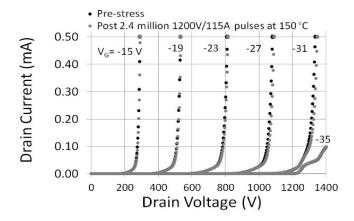

Specialized edge termination structures, such as multiple junction termination extensions and floating guard rings, were fabricated and maximized high-voltage performance [12]. Ruggedness and reliability demonstrations build confidence in SiC system insertion: a SiC JFET subjected to over 2.4 million 1200-V hard-switching events at 13 times its 150 °C rated current showed no electrical characteristics degradations (see Fig. 5) [13]. SiC Schottky barrier diodes, planar and trench MOSFETs, and JFETs are commercially available as discrete components in the voltage range of 650–3300 V from several U.S., European, and Asian suppliers. Suppliers also provide modules with multiple transistors and high currents. The 3.3-kV MOSFETs became commercially available from a large manufacturer in 2022. Historically, a 1200-V SiC MOSFET, released by Cree in 2011, was the first commercial

225

227

228

229

230

232

233

234

236

238

240

242

243

244

247

248

249

251

253

255

257

258

259

Fig. 5. Blocking voltage JFET curves before (black circles) and after (gray circles) more than 2.4 million hard-switching events at  $150\,^{\circ}$ C and at 13 times the JFET's rated current. The blocking voltage characteristics are measured at  $25\,^{\circ}$ C and are unchanged.

SiC transistor [14]. Today, the SiC MOSFET is the dominant SiC switch used in power electronics.

SiC power transistors have been commercially available since 2011 and have steadily gained market share. However, high device cost and reliability/ruggedness concerns are barriers in their mass adoption. In several applications, such as PV systems, insertion of SiC reduces overall system cost compared to Si even though SiC devices cost two to three times more than their Si counterparts. This is due to the passive and cooling system simplifications enabled by SiC high-frequency operation. Still, reducing SiC device costs is highly desirable. The SiC wafer represents 45%-65% of the overall SiC device cost, a consequence of the unique substrate fabrication specifics outlined in the discussion of Fig. 2. A SiC device cost reduction of over 20% is expected with the transition from 150- to 200-mm substrates. Further cost reductions can occur with SiC device manufacturing in fabs alongside Si. SiC devices fabricated in large Si volume fabs exploit economies of scale that lower costs. Through repurposing mature fully depreciated 150- and 200-mm Si fabs, SiC power devices can be manufactured with the relatively small investments necessary to support unique SiC processing steps, such as high-temperature implantation and anneal, and ohmic contact formation. Minimizing fabrication cost by exploiting the mature Si volume production assumes that the fab is loaded close to capacity with standard Si and SiC processes running on the same line. In addition, aggregating the demand for SiC substrates and epilayers in a few volume fabs contributes to lower material costs. Lower fabrication costs in a fully depreciated Si+SiC "capacity" loaded fab, coupled with decreased material costs, lead to significant price reductions for SiC devices. This approach offers a new opportunity for outdated Si fabs that have not kept up with the channel length reductions of the last two decades to continue manufacturing legacy Si parts while ramping up SiC fabrication that requires relatively modest  $0.3-\mu m$  design rules [15].

Material and fabrication improvements improve device yields and reliability. More planar wafers, reduction of BPDs and process-generated defects, and higher quality gate oxides that reduce threshold voltage instability are all being addressed. Valuable data are being accumulated over years of field operation and are analyzed to drive device optimization. Independent facilities that perform reliability analyses of SiC devices have been established and contribute to "SiC user confidence" [16].

SiC devices are made more rugged by leveraging design tradeoffs to increase short-circuit time, which could also have the negative outcome of increased resistance. By making use of intelligent and fast gate drives with prognostic and diagnostic functions, the circuit can be cut off within the short circuit capability of the device enabling safe operation that rivals those of Si [17], [18].

Finally, a workforce well-trained in SiC power electronics is the key to creating the large device demand that will spur mass manufacturing with its cost-lowering benefits. Entities such as PowerAmerica carry out university-/industry-applied collaborative projects, offer industry-driven WBG short courses and tutorials, and match students with internship opportunities [19]. These activities train the existing workforce and prepare future SiC technologists, ensuring accelerated deployment of SiC power electronics.

In summary, SiC system advantages over Si are summarized in bullet form as follows.

- 1) The large bandgap and critical electric field allow for high-voltage devices with thinner layers lowering resistance and associated conduction losses. This reduces capacitance enabling efficient higher frequency operation with reduced-size passive components.

- The large bandgap results in low intrinsic carrier concentration minimizing leakage and facilitating robust hightemperature operation.

- 3) The large thermal conductivity allows for high-power operation with simplified cooling management.

# B. GaN Devices

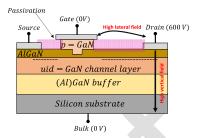

1) Lateral GaN: Present Advantages: GaN high electron mobility transistors (HEMTs) grown on Si substrates have advanced rapidly for low-voltage (typically <650 V) and highfrequency (up to 1 MHz and, in some cases, greater) power conversion applications [20]. Relatives of RF transistors, their chief advantage is perhaps their growth on inexpensive, largediameter Si substrates and their resulting compatibility with CMOS fabs. The increase in the distance between the gate and the drain in lateral devices will limit the application and use of GaN lateral devices for DER due to the cost increase resulting from the die size increase with increasing breakdown voltage. Nevertheless, lateral devices offer features that are well-suited for low-power applications (<10 kW). The 2-D electron gas (2DEG) of the GaN HEMT lateral device offers an outstanding low-resistive path for the charge carriers and bidirectionality. Lateral devices also have the advantage that the device current does not run parallel to extended defects in the epi growth, possibly making the achievement of the reliability related to these defects easier than for vertical devices. Finally, the lateral nature of the device facilitates the integration of multiple

AQ:11

261

262

263

265

267

269

271

272

273

274

275

276

278

279

280

28

282

284

286

288

289

290

291

292

293

294

295

298

300

301

302

303

305

307

309

311

313

364

365

366

368

370

372

374

376

378

380

381

382

383

385

387

389

391

393

394

395

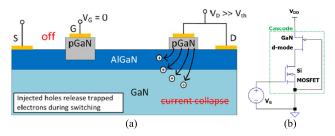

Fig. 6. Examples of (a) HD-GIT in an enhancement-mode configuration with a p-GaN gate and (b) circuit schematic for the setup of a cascode configuration with a depletion-mode GaN HEMT and an enhancement-mode Si MOSFET.

devices together within a single die and can enable the initial building of some logic functionality [21]. Although the logic would be limited to RTL or nMOS type, the complexity of the logic is only required to enable basic safety and drive functionalities. Thus, many low-power applications can take advantage of the integration benefit when the size/volume of the final product is of importance.

318

319

320

321

323

324

325

327

329

330

331

333

334

335

336

337

338

339

340

341

342

344

346

347

348

349

350

351

352

353

354

356

358

359

360

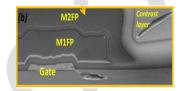

For those low-power applications where the total converter volume and weight are major driving factors, the performance of these lateral GaN power switches is second to none. Combining a much higher switching frequency (a  $5-10\times$ improvement over SiC devices) and lower ON-resistance due to the 2DEG channel creates a platform for significantly reducing the volume of passive components and the required heatsinking volume. In the past few years, the industry has been tasked with overcoming the reliability challenges associated with the poor reliability of normally-off GaN devices. There have been two prevailing commercial strategies for creating that normally-off capability for GaN HEMTs: a p-GaN gate or a cascode configuration. The p-GaN gated device is the only true enhancement-mode configuration between the two, and substantial progress has been made in reducing dynamic  $R_{\rm on}$  and increasing reliability for this device type. Advanced structures, such as the hybrid drain gate injection transistor (HD-GIT) [see Fig. 6(a)], have been demonstrated to fully eliminate current collapse phenomena [22], [23], [24]. However, depletion-mode HEMTs have inherently lower ONresistance; since gate reliability of GaN HEMTs can be an issue and is not considered as mature as their Si counterparts, a cascode combination [25] of a d-mode GaN HEMT with an e-mode Si MOSFET becomes an effective combination [circuit example shown in Fig. 6(b)]. At this time, several companies provide normally-off GaN FETs that are qualified to the stringent automotive standard (AEC-Q101), demonstrating that the challenges of reliability concerns for lateral GaN devices have been effectively mitigated.

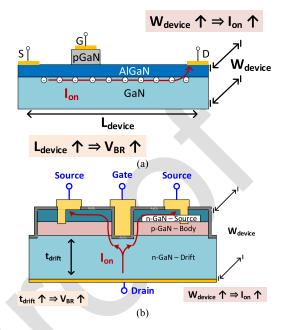

2) Future of GaN for High-Power Applications: Vertical Versus Lateral Architectures: DERs push the need for high-voltage, high-current, and compact power conversion systems. While small to medium levels of power generation may be appropriate applications for lateral GaN devices, larger power conversion systems (e.g., 100 kW–1 MW) require higher voltage devices with ratings of 1200 V or more [26]. This is required to minimize conduction loss, which is a significant factor in power conversion. Conduction losses are driven by

Fig. 7. Depictions of voltage and current scaling rules for both (a) lateral (HEMT) and (b) vertical (trench MOSFET) device architectures.

high current levels, so, by pushing to a higher conversion voltage for a given power level, current is reduced, and conduction loss is, in turn, minimized. Given these requirements, it is apparent that a vertical GaN device architecture is more suited to the higher power range of DER applications compared to a lateral architecture. Vertical device architectures allow for more efficient scaling to high-power levels by decoupling the current and voltage scaling into the x/y- and z-dimensions, respectively. In a lateral device, scaling to high voltage requires increasing the length from drain to gate, hence increasing the total area of the device. Likewise, increasing the current rating requires increasing the width of the device, also resulting in an increased area [see Fig. 7(a)]. High-voltage and high-current lateral devices become costly due to the large die area requirements as the current and voltage ratings increase. In contrast, in vertical device scaling, the voltage requires an increase in drift layer thickness (in the z-direction), which makes voltage scaling independent of the device area [see Fig. 7(b)]. In this way, vertical devices can be scaled to high power by decoupling the voltage scaling from the area of the die.

Both lateral and vertical GaN device types have the potential to carve out a space in the DER application sector, with lateral device architectures occupying more of the low-power space and vertical architectures occupying the high-power space. With that in mind however, at present, lateral GaN power transistors have reached a sufficient level of maturity for these devices to be considered for use in DER power conversion applications, while vertical GaN remains quite immature.

3) Vertical GaN: Device Types, Processing Challenges, and Future Development: Vertical GaN power devices are still relatively immature, with extremely limited commercial demonstrations and only a handful of research groups demonstrating successful device operation. However, the commercial availability of 2- and 4-in native GaN substrates has spurred

398

399

400

401

402

404

406

408

410

412

413

415

417

419

421

423

425

427

428

430

431

432

434

436

438

440

442

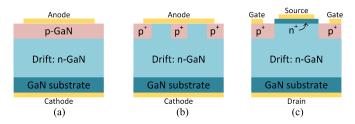

Fig. 8. Example architectures for (a) p-n diodes, (b) JBS diodes, and (c) JFETs.

interest and investment in this area, and significant progress has been made in recent years. A foundry process for vertical GaN p-n diodes is under development in the research community [27], and there has been a commercialization effort for junction field-effect transistors (JFETs) based on a vertical GaN architecture (see NEXGEN Power Systems [28]). However, neither p-n diodes nor JFETs are ideal device candidates for DERs. The p-n diodes [see Fig. 8(a)] have a large turn-on voltage and, as a result, are subject to reduced efficiency. A more suitable device is a junction barrier Schottky (JBS) diode [see Fig. 8(b)], which exhibits a low turn-on voltage like a Schottky diode but has a high reverse blocking voltage like a p-n diode. On the other hand, a major drawback for JFETs [see Fig. 8(c)] compared to MOSFETs is that a JFET is typically a normally-on device, which is a reliability and safety concern for most power electronic converters, while MOSFETs can be normally-off [29]. However, JBS diodes and MOSFETs pose unique challenges in terms of fabrication in GaN, including selective-area doping and electric field control within the device for both breakdown and reliability. As this field of research matures, the availability of these more advanced and complicated device types that are more suited to DER applications will increase, but, for now, it is limited to less-sophisticated and less-desirable devices, such as p-n diodes and JFETs.

Vertical GaN device development faces some critical challenges in developing robust high-voltage power devices. To achieve high breakdown voltages, proper attention should be paid to electric field management in the device, and electric field hotspots at the periphery of the device should be minimized. While there are several established edge termination methods for managing high fields in SiC devices, the most popular approaches rely on ion-implanted structures to spread the field. These edge termination methods for Si and SiC devices pose a challenge in GaN due to limitations in selective-area doping. Activation of implanted species in GaN, specifically the p-type dopant [Mg], requires high annealing temperatures approaching or exceeding 1300 °C, which causes the decomposition of GaN at atmospheric pressure. As a result of challenges with selective-area doping, creating some of these more complicated device architectures requires complex epitaxy employing etch-and-regrowth methods. Despite these concerns, vertical GaN p-n diodes have been demonstrated with blocking voltages over 5 kV [30], showing great potential for future devices. There is more work to be done to push the blocking voltage higher, and achieving ultralow doping in the drift region is no small task. Compensating defects in the epitaxy are a roadblock to creating drift regions with doping levels below  $1 \times 10^{15}$  cm<sup>-3</sup> although progress is being made in this area to enable vertical GaN devices capable of >5-kV blocking capability. As development efforts continue and demonstrations of >5-kV GaN devices appear in the near future, the promise of vertical GaN for higher power DER applications will grow stronger. For today, vertical GaN remains significantly behind SiC, and its development will take time to reach maturity.

445

446

447

448

449

450

452

453

454

455

456

457

458

459

461

463

464

465

467

469

470

471

472

473

474

476

478

480

482

483

484

485

486

487

488

489

490

491

492

493

494

495

496

497

When considering the development and eventual adoption of vertical GaN, these devices must broadly compete with existing SiC devices or be relegated to niche applications (e.g., 20-kV surge arrestor [31]). In direct comparison, vertical GaN is expected to maintain all the general material-specific advantages over SiC: higher critical electric field, higher mobilities, higher saturation velocity, and so on. For specific structures, such as vertical GaN MOSFETs, three times higher channel mobilities are expected [32]. However, due to challenges with selective area doping, the MOSFET cell pitch for GaN may always lag behind SiC, which would make the advantage of GaN less compelling. In addition, for the extreme end of voltage and current, the lack of conductivity modulation and high-level injection effects in GaN makes SiC more attractive. Conductivity modulation is a useful tool to lower resistance in ultrathick (>200  $\mu$ m) epi layers, which cannot be achieved in GaN due to low carrier lifetimes. As more innovation occurs in the vertical GaN space, we may see additional solutions that improve the value proposition of vertical GaN.

In summary, an overview of the value proposition of vertical GaN is given as follows.

- 1) At the material and device levels, GaN retains several of the advantages of SiC summarized earlier.

- 2) In terms of materials, compared to SiC, vertical GaN yields modest material-based advantages (critical e-field, bulk mobility, and saturation velocity) and disadvantageous thermal performance.

- 3) Compared to SiC MOSFET, vertical GaN yields three times higher channel mobility that translates to a significant advantage for ON-resistance for voltage classes under 2 kV. In addition, for the latter, cell pitch is likely less favorable even with further maturation of GaN technology, and conductivity modulation and high level of injection are found lacking (which is disadvantageous for 10 kV and beyond).

- 4) Compared to lateral GaN (HEMTs), vertical GaN scales better for high voltage (>1.2 kV) and high current (>100 A). However, for the vertical GaN, the lack of a 2DEG implies that the operational switching frequency is likely ten times lower (50 kHz versus 500 kHz).

# III. ULTRAWIDE BANDGAP DEVICES

#### A. Advantages of UWBG PSDs Compared to SiC and GaN

The UWBG PSDs are an emerging class of materials that are loosely defined as having bandgaps larger than that of GaN, i.e.,  $E_G > 3.4$  eV. A comprehensive review of the UWBGs has been published, which describes many of the key issues for this

544

546

550

551

554

555

557

559

561

564

565

567

568

569

570

573

575

577

579

580

581

583

584

585

587

588

590

594

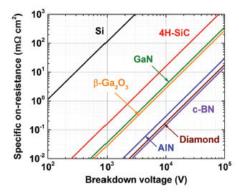

Fig. 9. Unipolar figure of merit for selected WBG and UWBG semiconductors. Reproduced from [33] with permission.

500

502

503

504

506

508

510

511

512

513

514

515

517

519

521

524

525

527

529

530

531

532

534

535

536

537

538

class of materials [33] (see Fig. 9), in addition to reviews specific to several UWBG materials [34], [35], [36]. Furthermore, the Office of Science within the U.S. Department of Energy has recently established an Energy Frontier Research Center focused on UWBG semiconductors, targeting their use in the future electricity grid [37]. While many materials fall into this category, the most mature are aluminum GaN (AlGaN), diamond (the cubic form of carbon), and beta gallium oxide (b-Ga<sub>2</sub>O<sub>3</sub>; other crystal structures are also possible). In addition, related UWBG materials include  $(Al_xGa_{1-x})_2O_3$ , cubic boron nitride (c-BN), transition-metal nitrides, and the II-IV nitrides. The UWBG semiconductors may have an advantage over SiC and GaN largely due to the scaling of their critical electric field for avalanche breakdown, which is generally accepted to follow a power law in bandgap  $E_C \sim E_G^m$  [38] (with m around 2) although the exact value of the exponent is the subject of debate [39]. This leads not only to the ability to fabricate PSDs with higher breakdown voltages (possibly many tens of kilovolts), but UWBG devices would also have lower ONresistance for a given blocking voltage, as dictated by the unipolar figure of merit [40]. This essentially is the same advantage that SiC and GaN have over Si but extended to the next generation of materials. This is illustrated in Fig. 9. From the FOM, a diamond shows the potential to be an ideal material for high-power electronics, as the combination of ultrahigh breakdown field and high thermal conductivity is rare in a semiconductor. Diamond diode projects have demonstrated an increase in power density by at least 30× compared to that of SiC and GaN.

# B. Challenges for UWBG Semiconductors

While the UWBG materials have great potential, they are still immature, and numerous challenges exist related to their growth and processing, not to mention the eventual scaling of their fabrication to economical large-scale production. While native AlN, diamond, and Ga<sub>2</sub>O<sub>3</sub> substrates are available, only for the latter are these substrates routinely produced in large diameters at low process cost. Indeed, the availability of high-quality, n-type Ga<sub>2</sub>O<sub>3</sub> substrates (due to their ability to be grown from the melt) is one reason that devices made from this material have been heavily researched. While there is nothing fundamental that should stop single-crystal diamond

substrates from scaling, the efforts have been painstakingly slow. This raises concerns about the potential use of diamond as a scalable semiconductor. However, it should be noted here that foundries are coming up with ambitious but practical solutions that can handle small-size wafers [41].

Beyond substrates, a key challenge for all UWBG semi-conductors is impurity doping, which is asymmetric, meaning that doping of one type is much more difficult to achieve than doping of the other type. This is because the dopant atom of one type is typically very deep in the bandgap. For AlGaN, p-type doping is difficult across the entire compositional range [42], and for AlN ( $E_G \approx 6.2$  eV), it is practically impossible, as the Mg dopant is 0.5 eV deep in the gap and, hence, is a deep level rather than a shallow dopant. Even n-type doping is difficult for Al compositions x greater than about 0.85. For diamonds, the situation is the opposite, with n-type doping being extremely difficult to achieve. Finally,  $Ga_2O_3$  cannot be p-type doped at all, eliminating the possibility of fabricating bipolar devices.

Other challenges exist as well. For example, ohmic contacts are extremely difficult to form on UWBG semiconductors due to the high potential barrier that forms between the semiconductor and most metals [43]. This can conversely be advantageous when forming Schottky gates to HEMTs and similar structures. In alloyed materials such as AlGaN, alloy scattering reduces low-field mobility. However, this too can be advantageous because, even though the mobility and, consequently, the current density are low, they are also insensitive to temperature, enabling stable operation over a wide temperature range [44]. Alloying can also reduce the thermal conductivity in AlGaN, and the thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is quite low due to its complex crystal structure.

# C. UWBG Device Results

Despite the challenges outlined above, various devices have been demonstrated in several of the UWBG semiconductors. For Ga<sub>2</sub>O<sub>3</sub>, this has been largely enabled by the availability of large-area n-type substrates as noted above, and demonstrated device types include Schottky diodes, MOSFETs, and MESFETs [35], [36]. In Al-rich AlGaN, most device demonstrations to date have been HEMTs and related structures although some vertical devices, such as p-n and Schottky diodes, have also been reported [34]. Diodes have also been demonstrated in diamonds [45], in addition to lateral transistors using surface doping. Recent advances in diamonds have demonstrated n-type doping by phosphorus. In addition, ptype diamond is readily available, and these two successful doping schemes establish the potential of vertical p-n-p and p-n-i-p power devices based on homoepitaxial diamond layers. The ARPA-E SWITCHES effort demonstrated p-i-n diodes blocking up to 1 kV [46]. The NASA HOTTech program led to the demonstration of high-temperature operation (up to 650 °C) of diamond diodes [47], checking yet another important box that will impact power electronics. In general, all these devices are research prototypes, and more work is needed on the fundamentals of the UWBG materials and their processing into devices before they can be considered practical

553 AQ:12

599

600

601

602

603

604

605

606

607

609

611

613

615

617

618

619

620

621

622

623

624

625

626

628

630

632

633

634

635

636

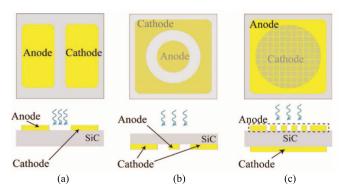

Fig. 10. PCSS in (a) lateral or in-line, (b) radial, and (c) vertical geometry configuration [48].

contenders for use with DERs. Nevertheless, if they mature sufficiently, they will hold great promise for very dramatic improvements in distributed energy systems.

#### IV. OPTICALLY ACTIVATED PSDS

#### A. Photoconductive Semiconductor Switch

PCSS technology has been under development for several decades, beginning with Si, then GaAs, and recently with WBG and UWBG materials. These devices are typically made of semi-insulating semiconductors that are triggered using an incident light pulse, typically from a laser, although electron beams have been reported in the case of diamonds. PCSS can be split into two broad categories: linear and high gain. In a linear PCSS, one electron is created per absorbed photon, and the device conducts current in an ohmic behavior when illuminated. In a high-gain PCSS, an avalanching process is typically employed, and many electrons are created per incident photon. Linear PCSSs have the advantage of greater control and reliability, while high-gain PCSSs reduce light requirements. Furthermore, PCSS is classified as intrinsic or extrinsic. An intrinsic PCSS uses above band gap light to create carriers, while an extrinsic PCSS uses below band gap light to generate carriers from deep-level dopants. In general, the strengths of PCSS devices can be summarized as follows: 1) simultaneous triggering of multiple PCSS using the same optical source (minimal jitter); 2) arbitrary high voltage and current are achieved (at the cost of increased laser size); and 3) extremely fast turn-on and turn-off times compared to comparably rated electronic devices.

Several geometries have been tested for varying applications, including lateral, radial, vertical with top illumination, and edge with side illumination. The first three geometries are outlined in Fig. 10. There are also vertical geometries with edge illumination, in which the optical input is fed through the side of the PCSS. The most widely implemented mode of PCSS is the linear operation, characteristic of linear output with input optical power. Table I summarizes PCSS linear mode operation from the literature with metrics encompassing ON-time (Ton), leakage current (Ileak), peak current (Imax), maximum blocking voltage (Vmax), and current slew rate (dI/dt). SiC PCSS shows exceptional power handling capability, while GaAs PCSS show exceptional turn-on times capable of sub-ns.

Fig. 11. Quenched high-gain PCSS operation [54].

TABLE I

SURVEY OF PCSS OPERATING IN THE LINEAR MODE

| Ref. | Material | Geometry        | Ton  | Ileak | Imax | Vmax | dI/dt   |

|------|----------|-----------------|------|-------|------|------|---------|

|      |          |                 | [ns] | [nA]  | [kA] | [kV] | [kA/µs] |

| [48] | 6H SiC   | Vertical        | 2    | 10    | 1.5  | 17   | > 100   |

| [49] | 4H SiC   | Lateral/In-line | 10   | 300   | 0.2  | 10   | 20      |

| [50] | 4H SiC   | Radial          | 4    | 4000  | 1    | 30   | > 100   |

| [51] | GaAs     | Lateral/In-line | 0.2  | NR    | 0.25 | 1.7  | 1250    |

| [52] | GaAs     | Lateral/In-line | 80   | NR    | 3    | 30   | 37      |

| [53] | GaN      | Lateral/In-line | 0.16 | NR    | 0.02 | 40   | > 100   |

638

639

640

642

644

646

648

649

650

652

653

654

655

657

659

661

663

664

665

667

Additional modes of operation have been explored in PCSS to achieve higher output power for a given input optical power. These high-gain modes of operation involve negative differential mobility (NDM) materials, whereby, after a certain electric field, the mobility drops rather than increases. NDM leads to the formation of charge carrier domains called Gunn domains that result from a field screening effect causing an accumulation of charge that can propagate throughout the material until it is collected at the opposing contact. The lock-on mode of operation is a phenomenon, whereby the switch voltage persists even after optical excitation has ceased and is independent of the charge voltage if it is above the lock-on entry threshold, which is very close to the NDM threshold. Lockon devices typically have low reliability, repeatability, and longevity due to destructive current filaments, which almost always accompany lock-on. Avalanche mode of operation occurs close to the semiconductor breakdown field allowing high gain due to impact ionization. PCSS operation and reliability in the avalanche mode are not well documented. The high-gain modes of operation are outlined in Table II, where GaN values are predicted by numerical simulation and not experimentally demonstrated. In Table II, the threshold is the field required for the mobility to begin decreasing, and the entry threshold is the field required to initiate lock-on behavior, while the closed state field is required to maintain it, and the avalanche entry threshold is the field required for the avalanche to begin.

A literature survey of high-gain PCSS is summarized in Table III. In addition to the parameters from Table I, we include latency, which relates to the time needed for the nonlinear mode to take effect after triggering. GaAs

695

697

699

701

702

704

706

708

710

712

713

714

715

716

718

719

720

721

723

727

730

731

732

733

734

736

738

740

742

745

746

747

TABLE II

DIFFERENT OPERATION MODES OF HIGH-GAIN PCSS

| Mode      | Fields across switch       | GaAs         | InP     | GaN                |

|-----------|----------------------------|--------------|---------|--------------------|

| NDM       | Threshold [kV/cm]          | 3.5          | 10      | ~150               |

| Lock-on   | Entry threshold [kV/cm]    | 3.5-8        | 15      | 150<br>(predicted) |

| LOCK-OII  | Closed-state field [kV/cm] | ~4-8         | 14      | 138<br>(predicted) |

| Avalanche | Entry threshold [kV/cm]    | ~20-25       | ~500    | ~5000              |

|           | Closed-state field [kV/cm] | Like lock-on | Unknown | Unknown            |

$\label{thm:constraint} \textbf{TABLE III}$  Survey of PCSS Operating in the Nonlinear Mode

| Ref. | Material | Mode                 | Geometry | Latency | Ton  | Ileak | Imax | Vmax | dI/dt   |

|------|----------|----------------------|----------|---------|------|-------|------|------|---------|

|      |          |                      |          | [ns]    | [ns] | [nA]  | [kA] | [kV] | [kA/us] |

| 27   | CaAa     | Lock-on              | n Ino    | Small   | 0.3  | NR    | 0.7  | 3.5  | 2300    |

| 21   | GaAs     | Avalanche            |          | 0.5-50  | 0.44 |       | NR   | 35   | NR      |

| 45   | GaAs     | High-                | In-line  | 5-20    | 3    | NR    | 0.09 | 4.5  | 30      |

|      |          | gain*                |          |         |      |       |      |      |         |

| 46   | GaN      | Lock-on <sup>+</sup> | 1D model | NR      | 0.16 | NR    | 0.02 | 40   | > 100   |

- \* High-gain mode is passively quenched before lock-on can initiate

- + Numerical study, not experimentally demonstrated

Fig. 12. Theoretical numerical study of lock-on in GaN from [55], [56], and [72].

can achieve exceptional turn-on times in both lock-on and avalanche modes. Shi et al. reported rapid quenching of the lock-on mode enabling high gain without the effects of current filamenting, as shown in Fig. 11. GaN is also predicted to have exceptionally fast turn-on times in the lock-on mode, as shown in Fig. 12.

UWBG materials offer the potential for substantially improved performance with reduced illumination intensity. However, due to their exceptionally wide band gaps, no practical laser sources exist for band-to-band illumination. Of these materials, diamond is the most studied, but reports are sparse. Polycrystalline diamond has been illuminated with both visible and ultraviolet illumination but is likely not suitable for high-power applications due to its poor electronic properties. Single-crystal diamond has been illuminated with an electron beam, analogous to the laser but also impractical. Recently, Hall et al. demonstrated an N-doped diamond PCSS with comparable responsivity compared to SiC.

## B. GaN PCSS

GaN is a promising WBG material [30], [57], [58] and offers important expected improvements in power device performance, including lower switching losses [59], higher

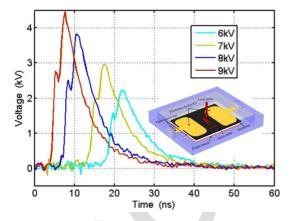

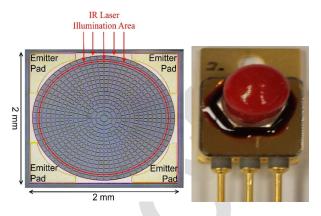

frequency operation [60], and higher power density, leading to systems with lower size, weight, and power (low-SWaP). For GaN PCSS devices, researchers have evaluated GaN as a candidate material and find it highly motivating because of the advantageous material characteristics, including increased breakdown fields of ~3 MV/cm, large electron peak drift velocity of >2.5 E7 cm/s, the high volumetric heat capacity of  $\sim 3$  J/cm<sup>3</sup>K, and large simulated photoconductive power gain of ~30 TW/J [61]. Researchers have successfully predicted and/or demonstrated GaN PCSS operating in the linear mode [62], [63], [64] using Fe- or C-doped GaN material to render the material semi-insulating for increased blocking voltages in the OFF-state. Early PCSS devices were used to generate THz or near THz radiation. These devices, fabricated in lateral and vertical geometries, demonstrated fast switching times of  $\leq 10$  ns, often limited by circuit and/or laser trigger performance with results indicating the carrier recombination lifetime to be <1 ns [53], and investigated the change in material resistivity between the ON- and OFF-states (greater than  $10^8$ ) to evaluate the prototype switches [53], [65]. Lateral device geometries used surface electrodes spaced with varying gap distances of tens of micrometers less than 2 mm with designs, including constant gaps, annular, and interdigitated configurations.

Vertical devices were made using large, mm size, and top and bottom contacts on thick ( $\sim$ 0.4 mm) semi-insulating substrate materials. These important results, while promising, often demonstrated lower than predicted voltage holdoff performance based on material parameters likely due to material or surface defects, electric field design, or device fabricationinduced imperfections limiting the performance. With continued efforts, material improvements, and fabrication and design improvements [66], [67], the linear mode switch performance has improved with demonstrated higher holdoff fields as high as 1.6 MV/cm being demonstrated [68]. In addition, experiments were conducted to understand and predict the wavelength-dependent behavior of the triggering mechanism showing the expected band-edge absorption mechanism of the material and including studies looking at subbandgap triggering for extrinsic (defect-induced) carrier generation in the material. Optical trigger sources used in these studies were typically Nd:YAG lasers with frequency modifications, and the wavelengths used included near or above bandgap (266-355 nm) and below bandgap (532 nm) energies with the largest photoresponse in linear switches seen with near or above bandgap wavelengths. Pulse energies in the mJ range were used, and energy densities were not systematically reported and hence difficult to compare.

Previous GaAs-based PCSS was demonstrated in the non-linear operating mode in both linear [69] and vertical geometries [70], where current flows after the termination of the external optical source. This has obvious implications for the switching mode efficiency as the requirements on the optical triggering energy are greatly reduced. Because of the advantageous material characteristics of GaN, the possibility of nonlinear or high-gain mode operation of GaN PCSS devices is of particular interest to scale switch voltages and power densities, especially when compared to GaAs devices.

AQ:13 670

672

674

675

676

677

678

679

680

681

682

683

685

687

751

753

755

757

758

759

760

761

762

763

764

765

766

768

770

772

774

776

779

781

783

785

787

789

791

793

794

795

796

798

800

802

803

804

To date, no SiC-based nonlinear PCSS operation has been observed and may be related to the indirect bandgap of the material. The GaN PCSS nonlinear mode was predicted [56] with simulations showing the effect of trap or defect-related mechanisms for semi-insulating GaN, including native defects, such as gallium or nitrogen vacancies, which can act as acceptors or donors, and impurity-related defects, including C, Fe, or Mn, which act as acceptors to compensate the material resulting in high resistivity. The performance of the simulated switch is highly dependent on the energy level of the trap states and the trap density. However, the lowest fields predicted to observe nonlinear behavior, ~150 kV/cm, corresponded to the presence of mid-gap states. This is needed in trap-to-band impact ionization processes and corresponds well to the intentional impurities in semi-insulating GaN materials.

The first reported experimental demonstration of nonlinear GaN PCSS operation was observed with lateral devices having 0.6-mm gap spacings, showing the characteristic indicators of the nonlinear mode, such as nonlinear GaAs devices [71]. These include persistent conductivity after the optical signal is terminated, observation of nondamaging filamentary current channels, and ON-state lock-on fields across the device. Observations of nonlinear device operation were seen in semi-insulating materials with mid-gap traps with either Mn or Fe doping, and the threshold fields for the nonlinear operation were ~25 kV/cm, far below the surface breakdown fields of the device, and remaining lock-on fields of 3 kV/cm. Optical trigger energies of  $\sim 30 \mu J$  at 532 nm were used to trigger the nonlinear operation and were significantly lower than linear switch reports. Surface effects may also contribute to device operation as the nonlinear effect was not observed with the devices submerged in Fluorinert FC-70. More work is currently underway to understand the device performance and develop models to explain the physical mechanism of the GaN-based switch, which may be significantly different than the GaAs device switch operation.

Based on the successful demonstration of linear and nonlinear GaN PCSS devices, future work is focused on improving the device design and performance for voltage and current scaling to realize the GaN material advantages while improving and evaluating device reliability to be considered for field use. Perhaps, the most important to the realization of GaN PCSS devices is understanding the implications of available compact optical triggering sources to enable applications that are space-, weight-, and cost-sensitive.

Considerable work was done in GaAs devices [70], [72] to improve and understand reliability, and similar efforts are underway for the improvement of GaN devices. The main factors that influenced device lifetime in GaAs devices included electrical circuit properties containing the switch, the optical trigger properties, and the PCSS switch properties, themselves. Circuit properties governed the operating voltage and current of the PCSS, the pulsed waveform characteristics, and the design of the materials and peak electric field near the PCSS device. Optical trigger properties include the trigger source energy, energy density, pulse duration, and wavelength. The PCSS influencing factors included the physical layout of the switch, material properties, including intentional impu-

rities (doping) design and surface coatings, and electrical contact design, including electrode configuration, metallization scheme, and contact polarity. Traditional circuit design for PCSS characterization typically uses a pulsed and/or switched voltage source to apply the electric field across the device carefully synchronized with the optical trigger, and the PCSS performance is determined by the device performance combined with the impedance of the rest of the circuit. Novel designs are also being proposed and simulated to improve the PCSS performance including monolithically integrated PCSS and electrical power switch structure to improve the photoelectric-conversion efficiency compared to a traditional dc charged PCSS device [73].

മറമ

809

811

813

815

817

818

819

820

821

822

824

825

826

828

830

832

833

834

835

836

837

839

841

843

845

847

850

851

853

854

856

857

858

860

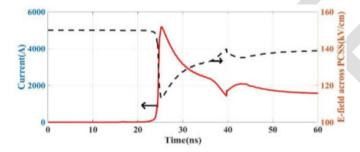

While understanding the switch characteristics is critical to improving device performance, the fielded applications for GaN PCSS devices will be ultimately limited by the availability of compact optical triggers. For example, one potential application for the ultrafast, nonlinear GaN switch is in the current commutation portion of a solid-state dc circuit breaker being developed under the ARPA-E BREAK-ERS program [74]. The proposed circuit breaker includes a normally-on leg through which the current from the system is conducted, a normally-off leg that is used to commute current from the system during a detected fault, and a shunt leg where the energy is dumped during a fault. The normally-on leg is composed of WBG semiconductor SiC transistor networks with balancing passive components all controlled by microprocessor-based controls and sensing electronics. The parallel, normally-off leg consists of the nonlinear GaN PCSS switch and a serially connected capacitor, and the shunt leg consists of an energy-absorbing element, such as a metal-oxide varistor. When a fault is detected, the normally-on leg is turned off coordinated with a synchronized dc biasing and triggering of the GaN PCSS to commute current from the system through the PCSS. Potential applications for this circuit breaker include opportunities, such as ship-based electrical systems, where size and weight are of critical importance, necessitating optimized designs for packaging, thermal management, and integration of a compact optical trigger source. Since the GaN PCSS performance depends on the optical trigger wavelength and energy, commercially available sources will be important, as well as the PCSS design. Intrinsic switches will need to be optically triggered with short (ns scale), high-energy ( $\mu J$ mJ) pulses from at or above bandgap sources with wavelengths of  $\sim$ 365 nm or shorter where low-cost, compact trigger options are limited. Alternatively, extrinsic switches can be triggered using optical wavelengths below the bandgap where optical source availability is more common including semiconductor-based laser diode options.

#### C. Optical Bipolar PSDs

While PCSS devices have seen significant research across different material bases, optical bipolar PSDs have shown promise for power-electronic applications [75]. This encompasses light-triggered thyristor (LTT) [76]. One of the key advantages of the LTT is the high electrical gain of the thyristor that significantly reduces the requirement for optical

887

888

889

890

891

893

894

895

897

899

900

901

902

903

904

906

908

910

911

912

913

915

917

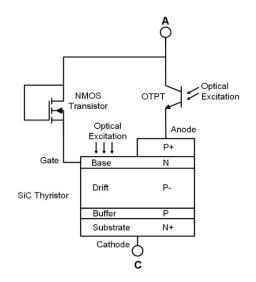

Fig. 13. Structure of an optical ETO and currents for the optical thyristor for one switching cycle.

power, which has economy of scale implications for WBG optical thyristors [77] However, the high gain of the LTT comes at the price of slow turn of time since the thyristor is a latched device.

863

864

865

867

869

871

872

873

874

875

876

877

878

880

881

882

884

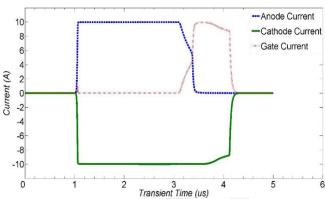

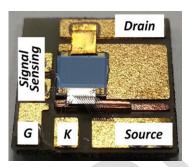

More recently, an optical emitter-turn-off thyristor (optical ETO) [78], [79], [80] has been outlined that overcomes this limitation of the LTT. Mojab and Mazumder [81] outline how this operational mechanism for controlling a single optical ETO can be extended for higher voltages using a series of two (or more) devices. As shown in Fig. 13, this is achieved using a low-voltage optically triggered power transistor (OTPT) [82], as shown in Fig. 14, and a low-voltage MOSFET that works mutually exclusively to turn the main optical power thyristor off using unity gain turn-off mechanism. While the optical bipolar PSDs outlined above serve as the main high-voltage power device, the low-voltage optical bipolar device can also be utilized for driving high-voltage field effect transistors. Mazumder [75] and Mazumder and Sarkar [83], for instance, illustrate how two low-voltage OTPTs can be used to control the charging and discharging switching dynamics of a SiC MOSFET. Similarly, optically triggered bipolar OTPT-based cascoded SiC JFET [84] has also been realized. Other structures based on GaN are also described in reference therein.

Fig. 14. Vertical experimental OTPT device geometry and actual package.

Fig. 15. Packages from the left to the right: XM3, HM, LinPak, and XHP.

#### V. PACKAGING

#### A. Wirebonded Modules

Commercially available wirebonded packages are optimized for Si devices rated for 650-V, 1.2-kV, 1.7-kV, 3.3-kV, and 6.5-kV applications. These modules are mainly available from Infineon, Vincotech, On Semiconductor, and Hitachi/ABB. Infineon offers IGBT half-bridge modules for all these voltage levels. Infineon offers 62-mm C-Series, EconoDUAL, PrimePACK, and pressfit EasyPACK 1B and 2B modules packages for 650-V, 1.2-kV, and 1.7-kV applications [85], [86], as well as XHP and IHV module platforms for 3.3- and 6.5-kV applications [87], [88]. Hitachi and ABB provide 62Pak and LoPak1 62-mm package platforms for 1.7-kV applications, and LinPak and HiPak packages for 3.3- and 1.7-kV applications [89], [90]. Vincotech has an EconoDUAL package in a 62-mm platform for the 1.2-kV IGBT module. SiC module manufacturers, such as Wolfspeed and Rohm, have utilized the 62-mm module platform and introduced HM [91] series and BSM [92] series for both 1.2- and 1.7-kV applications. Moreover, in the same 62-mm platform, CREE has its WAB [93] package for the same 1.2- and 1.7-kV applications. XM3 is a more compact package design for a 1.2-kV application [94]. Wolfspeed has even fabricated a module incorporating GaN Systems prepacked chip in their 62-mm HM series package [95]. Fig. 15 illustrates that the fabrication processes involved in these wirebonded power modules have relatively high maturity, while these modules offer power loop inductance anywhere from 9 nH up to more than 20 nH. This high commutation loop inductance could become a limiting factor for the application of high-power WBG devices.

Packaging plays an important role in ensuring the safe and reliable operation of semiconductor devices. With high-power

<sup>&</sup>lt;sup>1</sup>Trademarked.

Fig. 16. Hybrid package.

and increased switching speed, the selection of materials, interconnect technologies, and layout become more and more critical. Traditional power modules designed for Si IGBTs show their limitation when exposed to the faster switching speed and high-frequency operation enabled by the new generation of WBG power devices.

Power loop inductance introduces an inductive voltage spike across the device terminal during the hard switching operation. It curtails package reliability due to the increased propensity of partial discharge and insulation failure. The external preventive approach, such as reducing switching speed, harms efficiency by increasing the switching loss. Moreover, to increase the power handling ability of the module, multiple dies are required to parallel in a switching position. An asymmetric layout will lead to uneven dynamic current sharing between the paralleled dies. This will impose a transient temperature imbalance between them and may reduce the reliability of a particular device.

Thermal resistance determines the power handling ability of semiconductor devices. Poorly designed modules will often require extensive and bulky thermal management systems that will increase the cost and reduce power density. Layout, materials, and interconnect technologies have their individual impact on power loop inductance and thermal resistance. Most of the commercial power modules use wirebonds as interconnects from the top side of the semiconductor chips. It increases the area of the commutation loop and restricts the cooling from only one side of the package. Different endeavors have been reported to replace wirebonds to reduce loop inductances and thermal resistances. Some of them are discussed in detail next. Detailed discussion and guidance to choose materials for power modules are reported in the exiting literature [96], [97] and hence not repeated here.

To reduce the loop inductance while keeping the advantages of the maturity from the wirebonded module structure, researchers have proposed a "hybrid" structure (see Fig. 16) that combines the advantages of the maturity from the fabrication processes and the low inductances from multisubstrate vertical commutation loop structures. Wang et al. [98], Chen [99], and Chen et al. [100] have reported such a structure in different designs, respectively. All these works have achieved reduced loops' inductance compared to traditional wirebonded modules.

Fig. 17. SiPLIT interconnect technology.

Fig. 18. SKiN technology.

Fig. 19. DLB module package.

# B. Wirebondless Modules

Wirebond has its limitations and has been identified as one of the weakest points in modern module fabrication technology. Several endeavors have been taken and new technologies tried to replace the prone-to-failure wirebonds. Siemens introduced a planar interconnect technology (SiPLIT), as shown in Fig. 17. In this technology, Cu is deposited on high-insulating film to connect the top side of the die. Through electrical and thermal characterization, it was found that up to 50% reduction in parasitic inductances and a 20% decrease in thermal resistance were achieved [101].

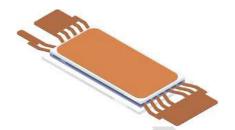

Semikron has brought this concept to another level and demonstrated its SKiN technology (see Fig. 18) as another interconnect technology to replace wirebonds. In SKiN technology, power chips are sintered to a DBC substrate, and another top side sintering of the power chips is done to a flexible printed circuit (FPC). This technology was introduced in 2011 and is now being used for SiC module packaging. It has shown that a loop inductance of as low as 1.4 nH can be achieved using this technology [102], [103].

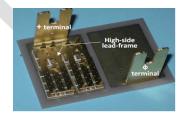

Another wirebond alternative is to use copper-clip interconnection and direct leadframe bonding (DLB), as captured in Fig. 19. Woo et al. [104] demonstrated this technology and used silver sintering to connect the Cu clip to the die, where copper clips can reduce the parasitic inductance and help to achieve better heat removal from the top side of the dies. Instead of using copper clips for "pad-to-substrate"

1038

1040

1042

1045

1047

1049

1050

Fig. 20. POL technology.

989

990

991

993

995

997

998

1000

1001

1002

1003

1004

1005

1006

1008

1010

1011

1012

1013

1014

1015

1017

1019

1020

1021

1022

1023

1024

1025

1026

1027

1028

1030

1031

1032

1033

1034

connection, Silicon Power Cooperation and STMicroelectronics demonstrated DLB on power devices. This package structure enables device-to-power terminal direct connection and, thus, can achieve reduced power loop inductance and top side cooling feature. General Electric developed a power overlay (POL) interconnect technology, as illustrated in Fig. 20, for Si and SiC packages [105]. In this package, the topside of the die is connected using a flexible substrate made of polyimide and copper. It reduces the parasitic inductance and increases the reliability of the module.

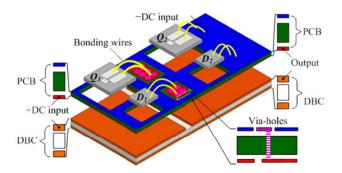

The development of 2.5-D and 3-D packages provides another pathway to further optimize the commutation loop inductance and achieve higher power density. Such a structure adopts multilayer DBC and vertical power-loop design in power modules and provides double-sided cooling capability with optimized low loop inductance. The 2.5-D design structure has two layers of metallization with the devices connected to the bottom DBC. The copper layer is etched to a desired pattern where the IGBTs and diodes are attached by soldering. The top metal connection and the bottom DBC can be connected through metal post interconnect [metal post interconnect parallel plate structure (MPIPPS)] [106], dimple array, and direct soldering/sintering (flip-chip on flex and embedded power) [107], [108], [109]. Similar designs can also be found in [110]. In 3-D modules, semiconductor chips are attached to two or more substrates, and the interconnection between them can be achieved through any technology. Hopkins et al. have proposed a prismatic module using flexible substrates and a connecting structure in the middle of the package [111]. Zhang et al. [112] used LTCC as a chip carrier sandwiched between two DBCs in a wirebondless SiC package.

Press-pack is a packaging approach that uses pressure contact as interconnect instead of wirebonding and soldering. Connections to the chips are made by physical contact pressure via external clamping between rigid electrodes and strain buffers. Zhu et al. [113] use fuzz buttons as spring contact. It shows reduced stress on the chip interface and enables double-sided cooling. Chang et al. [114] extend a similar concept from Aalborg University. PET films are used as insulators in between metal bars, while the whole package is kept together using bolts from each side.

Power chip on bus (PCoB) technology is another 3-D module design, and thick-finned copper acts as both heatsink and busbar. Power dies are electrically attached to two busbar-like power substrates directly. Molybdenum spacers are used as CTE buffers between the die and bottom substrates for reducing thermal-mechanical stress caused by CTE mismatch [115].

Fig. 21. Delphi 3-D packaged Viper module.

TABLE IV

Comparison Among Different Interconnects to Replace Wirebonds

| Packaging<br>Scheme | Properties, Pros, and Cons                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SiPLIT [101]        | <ul> <li>Thick copper on an insulating film is used as a topside interconnect.</li> <li>Reduction of power loop inductance by 50% and thermal resistance by 30% compared to traditional wire bonded packages.</li> <li>Increased power handling capacity and low switching loss and overshoot.</li> </ul> |  |  |  |  |  |

| SKiN [102]          | <ul> <li>Dies are sintered from top and bottom sides.</li> <li>Sintering improves the bonding reliability compared to solder-based joints.</li> <li>Very low power loop inductance (~ 1.4 nH)</li> <li>Reduced switching loss and overshoot</li> </ul>                                                    |  |  |  |  |  |

| DLB [104]           | Copper clips are used as top side interconnect.     Silver sintering is the attachment method, hence increased reliability compared to solder joints.     Reduced power loop inductance and thermal resistance                                                                                            |  |  |  |  |  |

| POL [105]           | Wire bonds are replaced with flexible substates.     Low power loop inductance reduced switching loss and overshoot.                                                                                                                                                                                      |  |  |  |  |  |

| Press Pack [113]    | Pressure contacts-based connection from top side of the dies instead of soldering/sintering     Reduced stress on the dies.     Low power loop inductance and thermal resistance.                                                                                                                         |  |  |  |  |  |

| РСоВ [115]          | <ul> <li>Double sided cooling enabled by 3D packaging structure.</li> <li>Low power loop inductance due to small loop area.</li> </ul>                                                                                                                                                                    |  |  |  |  |  |

The 0.5 °C/W thermal resistance and 8-nH loop inductance have been reported for this package.

These 2.5-D and 3-D packages provide both superior thermal and electrical performances, and thus, it has been adopted by the automotive industry as a trend for future advanced EV drives. Most of these modules in EV applications have transfer-molded packages and double-sided cooling features to be able to withstand the high-temperature operation environment. Hitachi [116], Delphi [117] (see Fig. 21), Toyota [118], ST Microelectronics [119], Mitsubishi [120], and Infineon [121] modules are now implemented inside the automobiles for different purposes and types of power conversion. Table IV provides a comprehensive summary of these interconnect technologies.

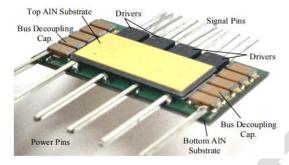

#### C. Advanced High-Voltage Power Module

The increasing development of distributed energy systems also poses strong demand for medium- and high-voltage power

1056

1058

1059

1060

1061

1062

1063

1065

1066

1067

1069

1070

1071

1072

1073

1074

1075

1076

1077

1078

1080

1081

1082

1083

1084

1085

1087

1088

1089

1091

1093

1094

1095

Fig. 22. 10-kV module from Aalborg University.

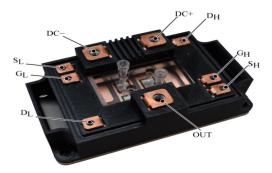

modules (>6.5 kV). Besides the commercially available packages, advanced designs for high-voltage module development are also in progress to support higher voltage and better performance. The U.S. Army Research Laboratory has a lot of research efforts in HV SiC diode and SGTO packaging using different structures, including using metal-tab interconnection, ceramic lid, and Kovar metal connection to achieve both low inductance and better thermal management, using printed ABS housing for enhanced insulation [122]. North Carolina State University [123] and CREE/Powerex [124] have been demonstrating their 10-kV designs in wirebonded power modules. These module designs require specific consideration of insulation, high electric field mitigation, and dV/dt-induced noise control. Virginia Tech has proposed another 10-kV module with stacked DBC and spring-loaded pins connection, and has used a CM noise screen to mitigate the CM noise generation from the module and achieved 13-dB reduction [125]. Munk-Nielsen et al. from Aalborg University have designed a 10-kV module in a single DBC substrate and optimized it for lower CM noise emission [126]. Deshpande et al. [127] proposed, as shown in Fig. 22, stacked DBC-based cavitated substrate for balanced E-field, voltage, and CM noise reduction from the 15-kV SiC module.